#### **INSTRUCTION MANUAL**

# RFL 9700 Digital Protection Channel

#### NOTICE -

The information in this manual is proprietary and confidential to RFL Electronics Inc. Any reproduction or distribution of this manual, in whole or part, is expressly prohibited, unless written permission is given by RFL Electronics Inc.

This manual has been compiled and checked for accuracy. The information in this manual does not constitute a warranty of performance. RFL Electronics Inc. reserves the right to revise this manual and make changes to its contents from time to time. We assume no liability for losses incurred as a result of out-of-date or incorrect information contained in this manual.

#### WARRANTY

Except where noted, all RFL Electronics Inc. products come with a one-year warranty from date of delivery for replacement of any part which fails during normal operation. RFL will repair or, at its option, replace components that prove to be defective at no cost to the Customer. All equipment returned to RFL Electronics Inc. must have an RMA (Return Material Authorization) number, obtained by calling the RFL Customer Service Department. A defective part should be returned to the factory, shipping charges prepaid, for repair or replacement FOB Boonton, N.J.

RFL Electronics Inc. is not responsible for warranty of peripherals, such as printers and external computers. The warranty for such devices is as stated by the original equipment manufacturer. If you have purchased peripheral equipment not manufactured by RFL, follow the written instructions supplied with that equipment for warranty information and how to obtain service.

#### **WARRANTY STATEMENT**

RFL Electronics Inc. products are warranted against defects in material and workmanship for one year from the date of shipment. During the warranty period, RFL will repair or, at its option, replace components that prove to be defective at no cost to the customer, except the one-way shipping cost of the failed assembly to the RFL Customer Service facility in Boonton, New Jersey.

This warranty does not apply if the equipment has been damaged by accident, neglect, misuse, or causes other than performed or authorized by RFL Electronics Inc. This warranty specifically excludes damage incurred in shipment to or from RFL. In the event an item is received in damaged condition, the carrier should be notified immediately. All claims for such damage should be filled with the carrier.

#### NOTE -

If you do not intend to use the product immediately, it is recommended that it be opened immediately after receiving and inspected for proper operation and signs of impact damage.

This warranty is in lieu of all other warranties, whether expressed, implied or statutory, including but not limited to implied warranties of merchantability and fitness for a particular purpose. In no event shall RFL be liable, whether in contract, in tort, or on any other basis, for any damages sustained by the customer or any other person arising from or related to loss of use, failure or interruption in the operation of any products, or delay in maintenance or for incidental, consequential, indirect, or special damages or liabilities, or for loss of revenue, loss of business, or other financial loss arising out of or in connection with the sale, lease, maintenance, use, performance, failure, or interruption of the products.

RFL Electronics Inc. Boonton, New Jersey USA

#### TRADEMARKS

"Amphenol" is a registered trademark of Amphenol Products, an Allied-Signal company.

"Fluke" is a registered trademark of the John Fluke Mfg. Co.

"Photodyne" is a registered trademark of Photodyne, Inc.

"Hewlett-Packard" is a registered trademark of the Hewlett-Packard Company.

"Switchcraft" is a registered trademark of Switchcraft, Inc.

"Z-80" is a registered trademark of Zilog, Inc.

The trademark information listed above is, to the best of our knowledge, accurate and complete.

# **CAUTION**

### FOR YOUR SAFETY

THE INSTALLATION, OPERATION, AND MAINTENANCE OF THIS EQUIPMENT SHOULD ONLY BE PERFORMED BY QUALIFIED PERSONS.

# **WARNING:**

The equipment described in this manual contains high voltage. Exercise due care during operation and servicing. Read the safety summary on the reverse of this page.

#### **SAFETY SUMMARY**

The following safety precautions must be observed at all times during operation, service, and repair of this equipment. Failure to comply with these precautions, or with specific warnings elsewhere in this manual, violates safety standards of design, manufacture, and intended use of this product. RFL Electronics Inc. assumes no liability for failure to comply with these requirements.

#### **GROUND THE CHASSIS**

The chassis must be grounded to reduce shock hazard and allow the equipment to perform properly. Equipment supplied with three-wire ac power cables must be plugged into an approved three-contact electrical outlet. All other equipment is provided with a rear-panel ground terminal, which must be connected to a proper electrical ground by suitable cabling. Refer to the wiring diagram for the chassis or cabinet for the location of the ground terminal.

# DO NOT OPERATE IN AN EXPLOSIVE ATMOSPHERE OR IN WET OR DAMP AREAS

Do not operate the product in the presence of flammable gases or fumes, or in any area that is wet or damp. Operating any electrical equipment under these conditions can result in a definite safety hazard.

# KEEP AWAY FROM LIVE CIRCUITS

Operating personnel should never remove covers. Component replacement and internal adjustments must be done by qualified service personnel. Before attempting any work inside the product, disconnect it from the power source and discharge the circuit by temporarily grounding it. This will remove any dangerous voltages that may still be present after power is removed.

# DO NOT SUBSTITUTE PARTS OR MODIFY EQUIPMENT

Because of the danger of introducing additional hazards, do not install substitute parts or make unauthorized modifications to the equipment. The product may be returned to RFL for service and repair, to ensure that all safety features are maintained.

#### **READ THE MANUAL**

Operators should read this manual before attempting to use the equipment, to learn how to use it properly and safely. Service personnel must be properly trained and have the proper tools and equipment before attempting to make adjustments or repairs.

Service personnel must recognize that whenever work is being done on the product, there is a potential electrical shock hazard and appropriate protective measures must be taken. Electrical shock can result in serious injury, because it can cause unconsciousness, cardiac arrest, and brain damage.

Throughout this manual, warnings appear before procedures that are potentially dangerous, and cautions appear before procedures that may result in equipment damage if not performed properly. The instructions contained in these warnings and cautions must be followed exactly.

#### RFL Electronics Inc.

### **TABLE OF CONTENTS**

| Title Page Warranty Trademarks High Voltage Warning Safety Summary Table Of Contents List Of Illustrations List Of Tables                                                                                                                                                    | i           | Section 4. MAINTENANCE                                                                                                                                                                                                                                          |                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Warranty                                                                                                                                                                                                                                                                     | ii          | 4.1. INTRODUCTION                                                                                                                                                                                                                                               | 4-1             |

| Trademarks                                                                                                                                                                                                                                                                   | ii          | 4.2 REMOVAL AND REPLACEMENT                                                                                                                                                                                                                                     | 4-1             |

| High Voltage Warning                                                                                                                                                                                                                                                         | iii         | 4.2.1 Planda Modules                                                                                                                                                                                                                                            | 1_1             |

| Cafatu Cumman                                                                                                                                                                                                                                                                | 111<br>67   | 4.2.1, Fing-In Modules                                                                                                                                                                                                                                          | 4 D             |

| Table Of Contents                                                                                                                                                                                                                                                            | IV.         | 4.2.1. Plug-In Modules                                                                                                                                                                                                                                          | 4- <del>2</del> |

| Table of Contents ,                                                                                                                                                                                                                                                          | V           | 4.2.5. KS-449 And X.21 interface raneis .                                                                                                                                                                                                                       | 4-2             |

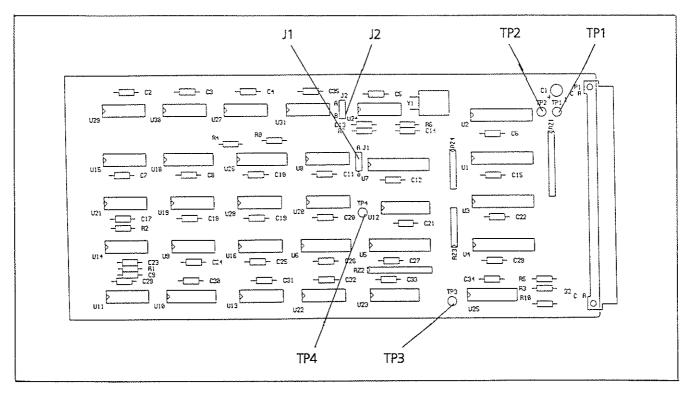

| List Of Illustrations ,                                                                                                                                                                                                                                                      | VII         | 4.2.4. Input/Output Module                                                                                                                                                                                                                                      | 4-3             |

| List Of Tables                                                                                                                                                                                                                                                               | ΙX          | 4.3. FUSE REPLACEMENT                                                                                                                                                                                                                                           | 4-3             |

|                                                                                                                                                                                                                                                                              |             | 4.4. CORRECTIVE MAINTENANCE                                                                                                                                                                                                                                     | 4-4             |

| Section 1. GENERAL INFORMATION                                                                                                                                                                                                                                               |             | 4.5. HOW TO ARRANGE FOR SERVICING 4                                                                                                                                                                                                                             | 4-4             |

| 1.1. PURPOSE OF THIS MANUAL                                                                                                                                                                                                                                                  | 1-1         |                                                                                                                                                                                                                                                                 |                 |

| 1.2. PURPOSE OF EQUIPMENT                                                                                                                                                                                                                                                    | 1-1         | Section 5. INPUT/OUTPUT MODULE                                                                                                                                                                                                                                  |                 |

| 1.3 FEATURES                                                                                                                                                                                                                                                                 | 1-1         | 5.1. DESCRIPTION                                                                                                                                                                                                                                                | 5-1             |

| 1.4. PHYSICAL DESCRIPTION                                                                                                                                                                                                                                                    | 1-2         | 5.1. DESCRIPTION                                                                                                                                                                                                                                                | 5-1             |

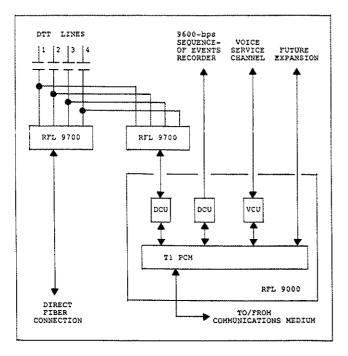

| 1.5. TYPICAL APPLICATIONS                                                                                                                                                                                                                                                    | 1-2         | 5.3. THEORY OF OPERATION                                                                                                                                                                                                                                        | 5-2             |

| 1.5.1 Polavino                                                                                                                                                                                                                                                               | 1-2         | 5,5. I) LONE OF OF EIGHTON                                                                                                                                                                                                                                      |                 |

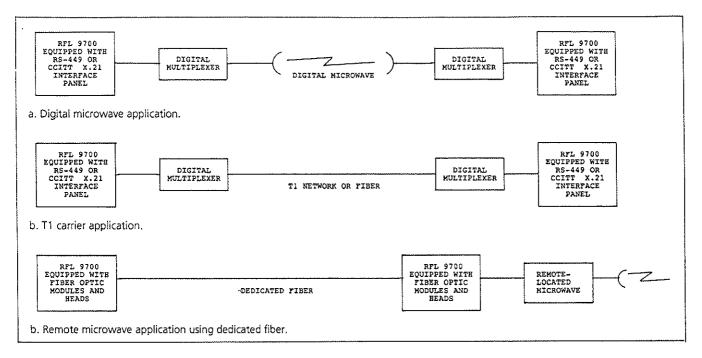

| 1.5.1. Relaying<br>1.5.2. Communication Interface                                                                                                                                                                                                                            | 1-2         | Coction & TDID BLIEFER MODULE                                                                                                                                                                                                                                   |                 |

| 1.5.2. Communication interface                                                                                                                                                                                                                                               | 1-2         | SECTION OF THE DOLLER MICHOLE                                                                                                                                                                                                                                   | c 1             |

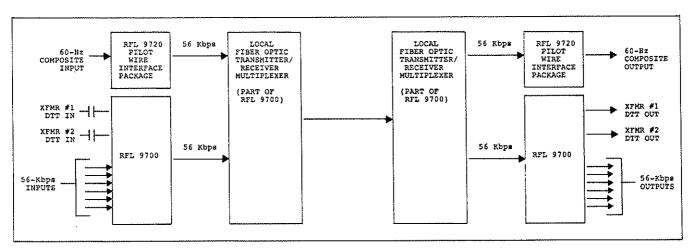

| 1.5.4. Fiber Optic Multiplexing                                                                                                                                                                                                                                              | 1-3         | 6.1. DESCRIPTION                                                                                                                                                                                                                                                | 0-I             |

| 1.6. SYSTEM SPECIFICATIONS                                                                                                                                                                                                                                                   | 1-3         | 6.2. SPECIFICATIONS                                                                                                                                                                                                                                             | b-1             |

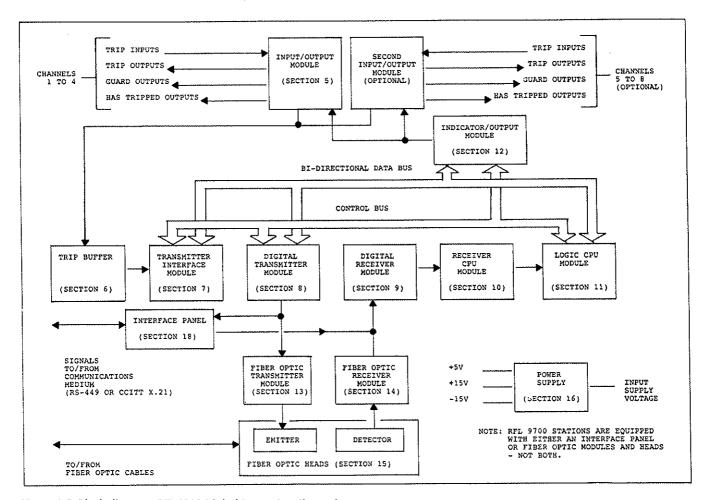

| 1.5.4. Fiber Optic Multiplexing 1.6. SYSTEM SPECIFICATIONS 1.7. RFL 9700 SUBASSEMBLIES                                                                                                                                                                                       | 1-5         | Section 6. TRIP BUFFER MODULE 6.1. DESCRIPTION                                                                                                                                                                                                                  | 6-1             |

|                                                                                                                                                                                                                                                                              |             |                                                                                                                                                                                                                                                                 |                 |

| Section 2. INSTALLATION 2.1. INTRODUCTION                                                                                                                                                                                                                                    |             | Section 7. TRANSMITTER INTERFACE MODULE 7.1. DESCRIPTION                                                                                                                                                                                                        | ~ 4             |

| 2.1. INTRODUCTION                                                                                                                                                                                                                                                            | 2-1         | 7.1. DESCRIPTION                                                                                                                                                                                                                                                | 7-1             |

| 2.2. UNPACKING                                                                                                                                                                                                                                                               | 2-1         | 7.2. SPECIFICATIONS                                                                                                                                                                                                                                             | 7-1             |

| 2.2.1. Individual Chassis                                                                                                                                                                                                                                                    | 2-1         | 7.3. THEORY OF OPERATION                                                                                                                                                                                                                                        | 7-1             |

| 2.2.2. Interconnected Chassis                                                                                                                                                                                                                                                | 2-1         |                                                                                                                                                                                                                                                                 |                 |

| 2.3. MOUNTING                                                                                                                                                                                                                                                                | 2-2         | Section 8. DIGITAL TRANSMITTER MODULE                                                                                                                                                                                                                           |                 |

| 2.3. MOUNTING                                                                                                                                                                                                                                                                | 2-2         | 8.1. DESCRIPTION                                                                                                                                                                                                                                                | 8-1             |

| 2.3.2. Interconnected Chassis Installed in                                                                                                                                                                                                                                   |             | 8.2 SPECIFICATIONS                                                                                                                                                                                                                                              | 8-1             |

| Rack Or Cabinet                                                                                                                                                                                                                                                              | 2-3         |                                                                                                                                                                                                                                                                 | 8-1             |

| 2.3.3. Interconnected Chassis Mounted On                                                                                                                                                                                                                                     | 2-3         |                                                                                                                                                                                                                                                                 |                 |

| Shipping Pails                                                                                                                                                                                                                                                               | ე_ <b>ე</b> | Section 9. DIGITAL RECEIVER MODULE  9.1. DESCRIPTION                                                                                                                                                                                                            |                 |

| Shipping Rails 2.4. VENTILATION                                                                                                                                                                                                                                              | 2-3         | O 4 DECEMBRICAL                                                                                                                                                                                                                                                 | 9-1             |

| Z.4. VENTILATION                                                                                                                                                                                                                                                             | 2-3         | 9.1. DESCRIPTION                                                                                                                                                                                                                                                |                 |

| 2.5. CUNNECTIONS                                                                                                                                                                                                                                                             | 2-3         | 9.Z. SPECIFICATIONS                                                                                                                                                                                                                                             | 9-1             |

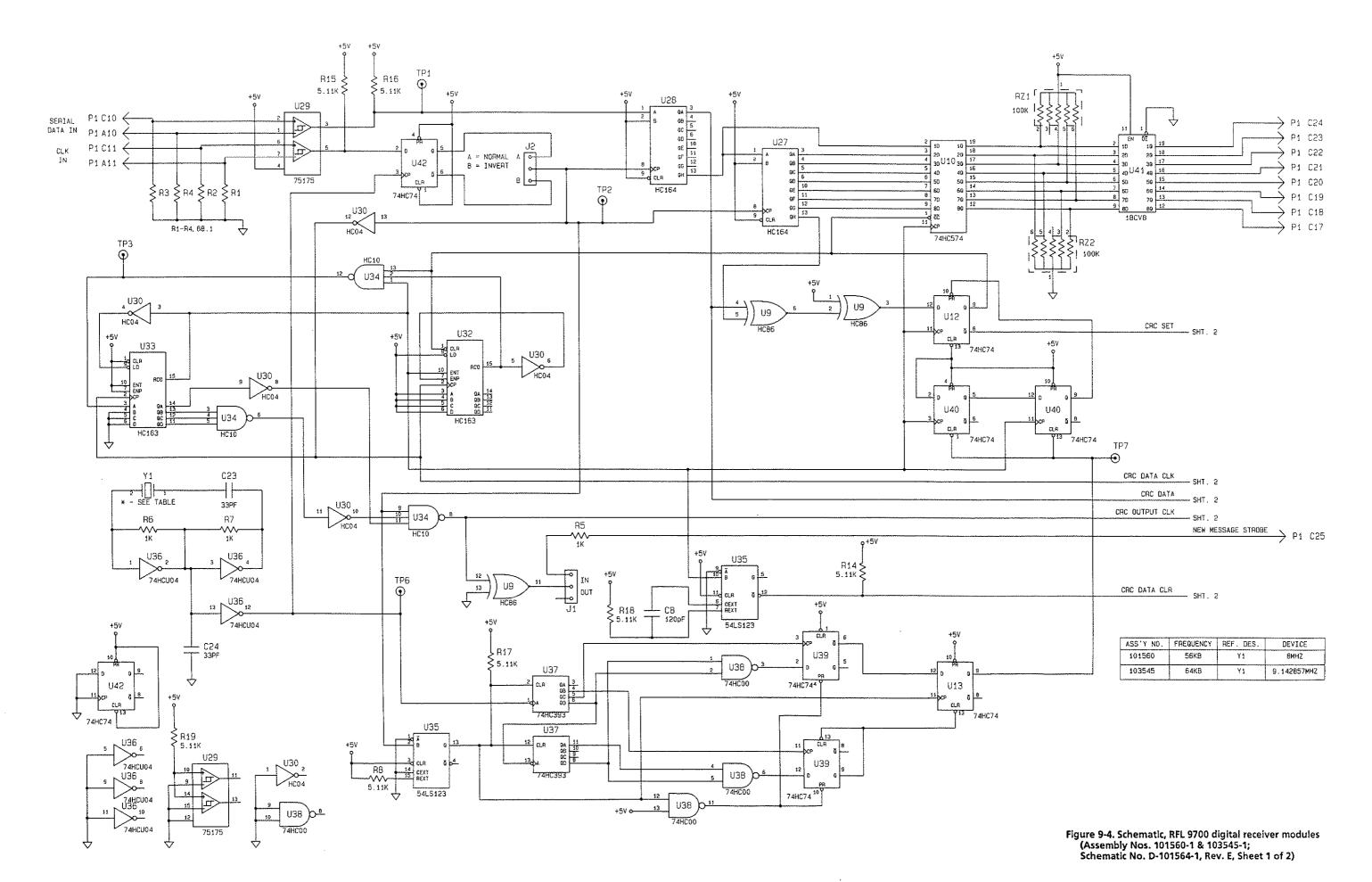

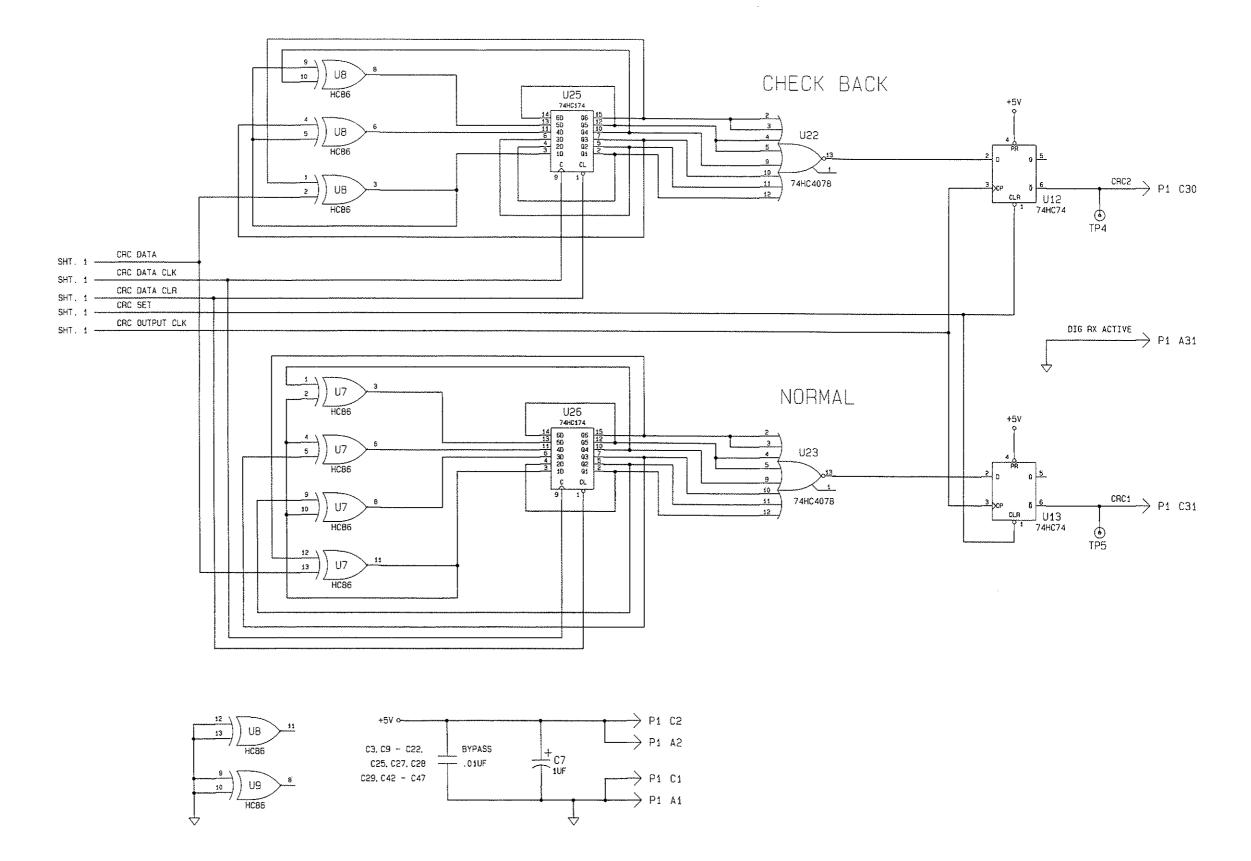

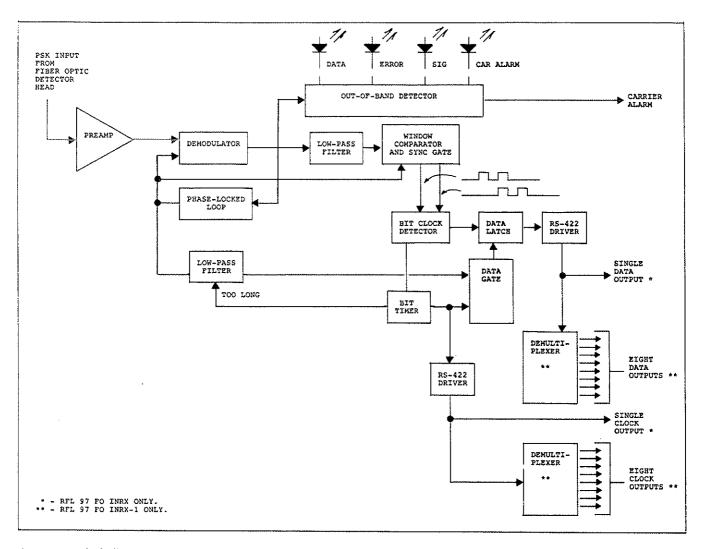

| 2.5.1. Making Connections To Terminal Blocks                                                                                                                                                                                                                                 | 2-3         | 9.3. THEORY OF OPERATION                                                                                                                                                                                                                                        | 9-2             |

| 2.5.2. Channel Input/Output Connections                                                                                                                                                                                                                                      | 2-5         |                                                                                                                                                                                                                                                                 |                 |

| 2.5.3. Alarm Relay Connections 2.5.4. Fiber Optic Connections                                                                                                                                                                                                                | 2-5         | Section 10. RECEIVER CPU MODULE 10.1. DESCRIPTION                                                                                                                                                                                                               |                 |

| 2.5.4. Fiber Optic Connections                                                                                                                                                                                                                                               | 2-6         | 10.1, DESCRIPTION                                                                                                                                                                                                                                               | 10-1            |

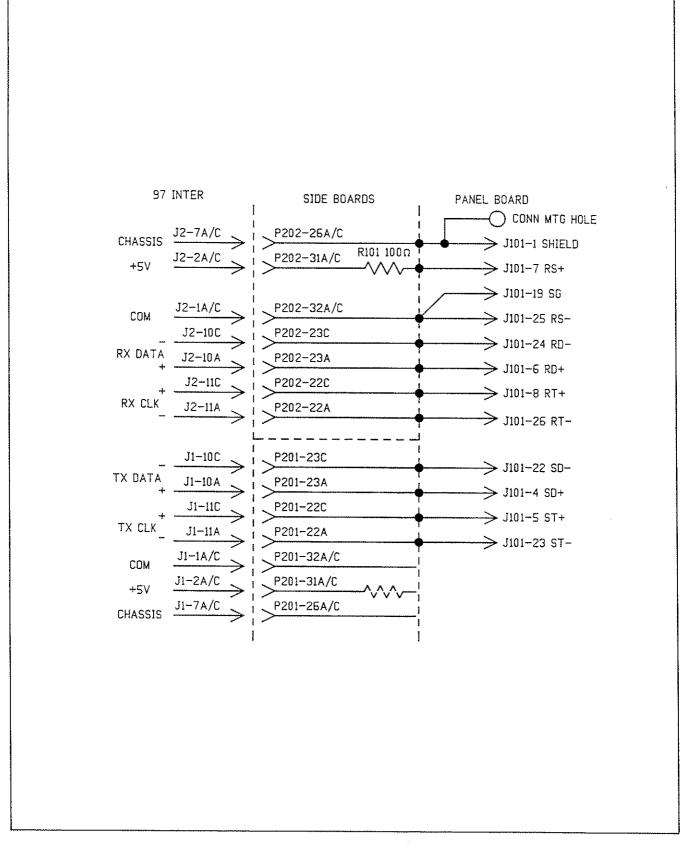

| 2.5.5. RS-449 And X.21 interface Connections                                                                                                                                                                                                                                 | 2-6         | 10.2. SPECIFICATIONS                                                                                                                                                                                                                                            | 10-1            |

| 2.5.6. Chassis Ground Connections                                                                                                                                                                                                                                            |             | 10.3. HARDWARE DESCRIPTION                                                                                                                                                                                                                                      | 10-1            |

| 2.5.7. Input Power Connections                                                                                                                                                                                                                                               |             | 10.3.1 Program Storage EPROM                                                                                                                                                                                                                                    | 10-2            |

| 2.5.7. Input to the confidence of                                                                                                                                                                                                                                            | - /         | 10.3.2 Static RAM                                                                                                                                                                                                                                               | 10-2            |

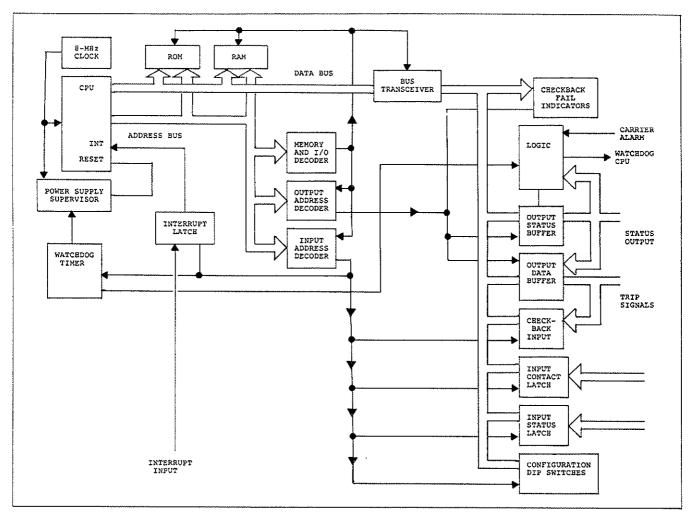

| Section 3. OPERATING INSTRUCTIONS                                                                                                                                                                                                                                            |             | 10.2.2. Microprosperor                                                                                                                                                                                                                                          | 10-2            |

| 2.4 PATRODUCTION                                                                                                                                                                                                                                                             | <b>→</b> 4  | 10.3.4. Address Describe                                                                                                                                                                                                                                        |                 |

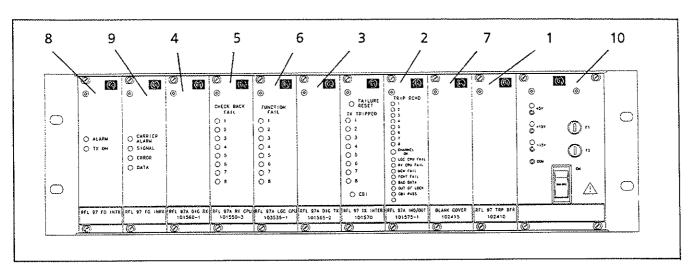

| Section 3. OPERATING INSTRUCTIONS  3.1. INTRODUCTION  3.2. CONTROLS AND INDICATORS  3.3. JUMPER AND SWITCH SETTINGS'.  3.3.1. RFL 97 TX INTER Module  3.3.2. Digital Transmitter Module  3.3.3. Digital Receiver Modules  3.3.4. CPU Modules  3.3.5. RFL 97 IND/OUT Module . | 5-1<br>5-1  | 10.1. DESCRIPTION 10.2. SPECIFICATIONS 10.3. HARDWARE DESCRIPTION 10.3.1. Program Storage EPROM 10.3.2. Static RAM 10.3.3. Microprocessor 10.3.4. Address Decoding 10.3.5. input Ports 10.3.6. Latches 10.3.7. Microprocessor Supervisor 10.3.8. Watchdog Timer | 10-3            |

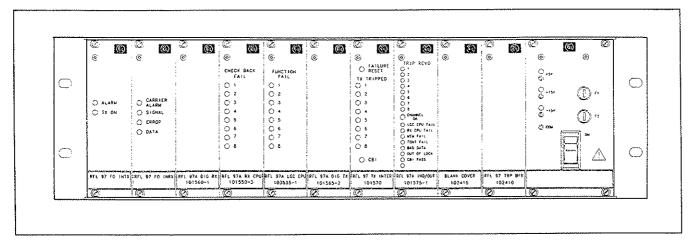

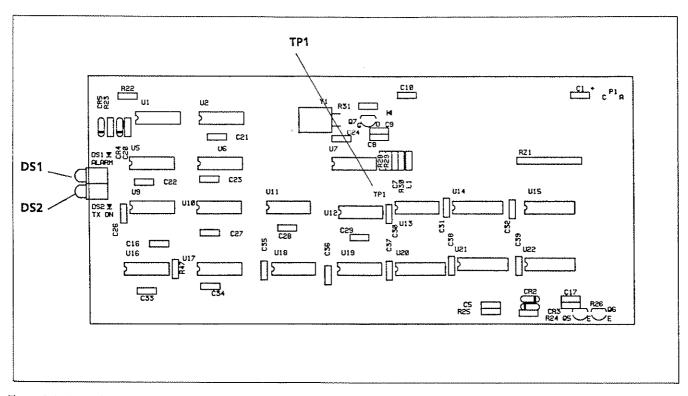

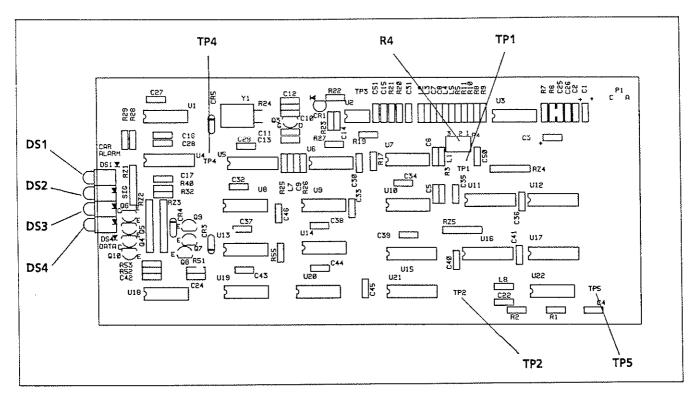

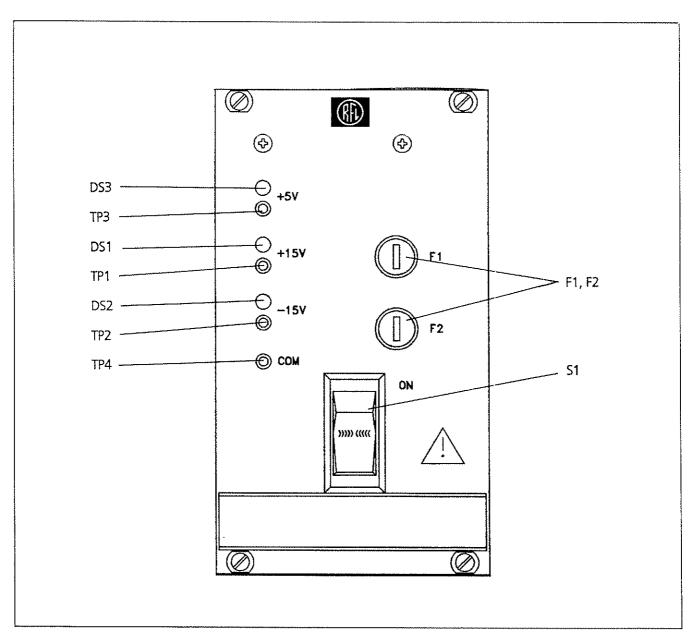

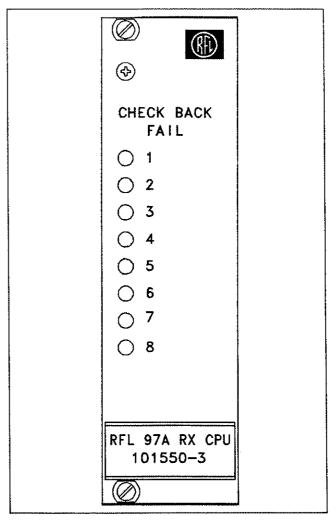

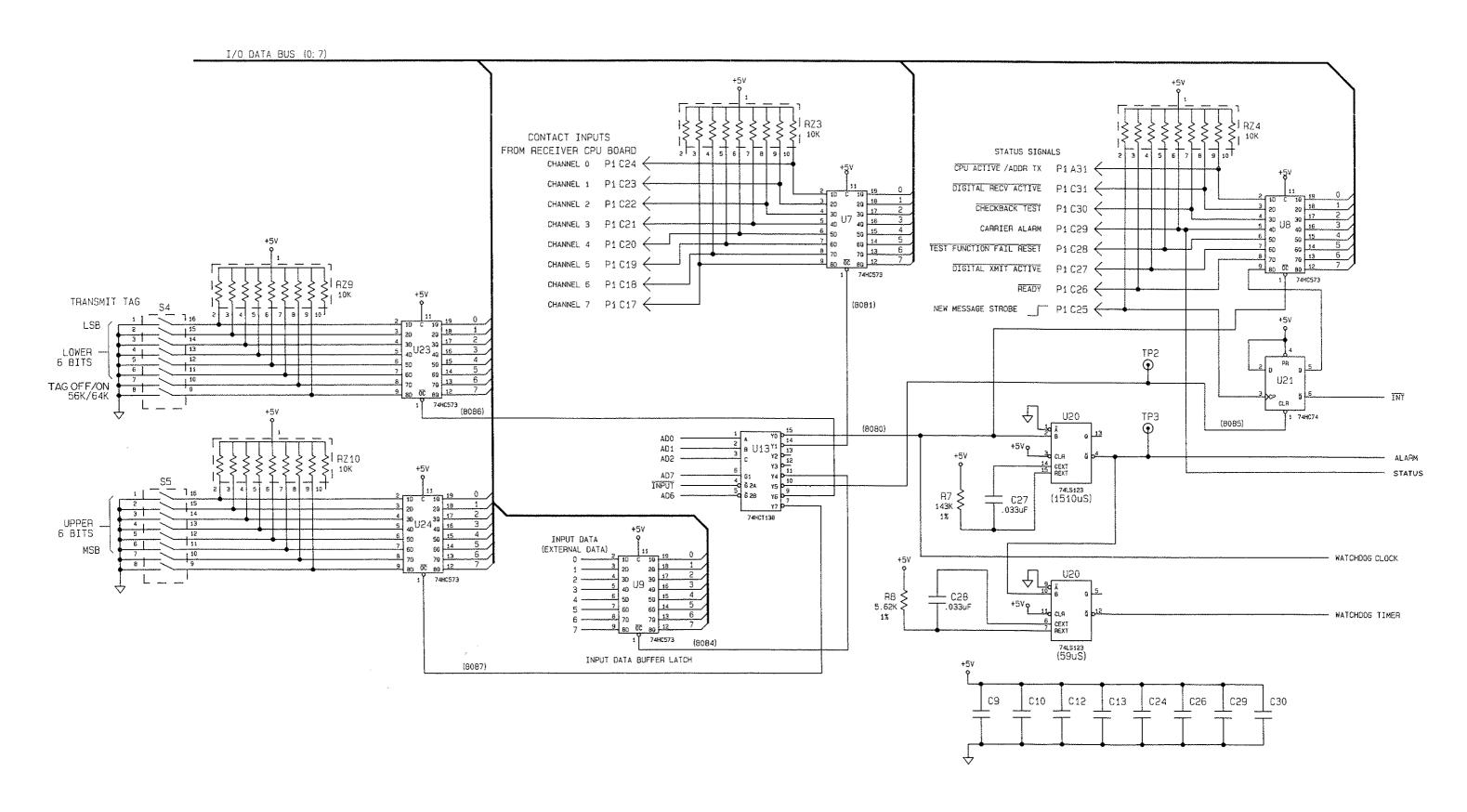

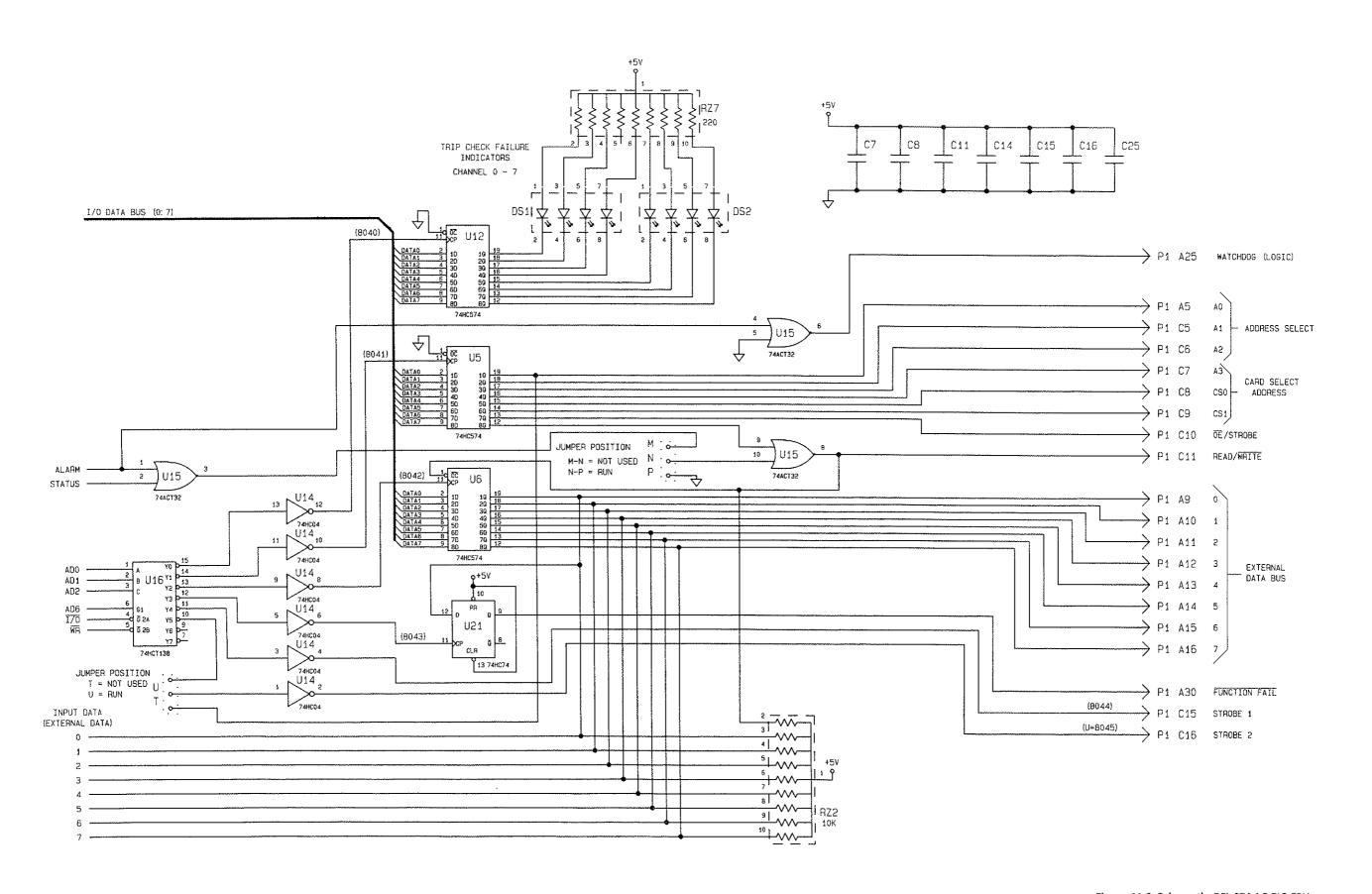

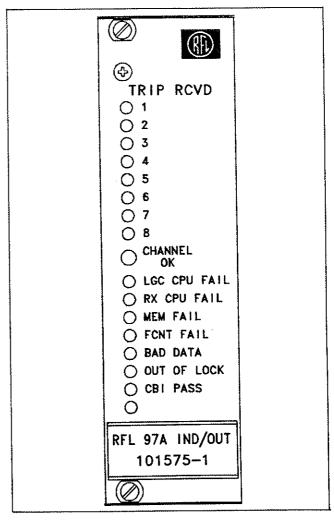

| 3.2. CONTROLS AND INDICATORS                                                                                                                                                                                                                                                 | 3-1         | 10.3.5. Input Ports                                                                                                                                                                                                                                             | 10-3            |

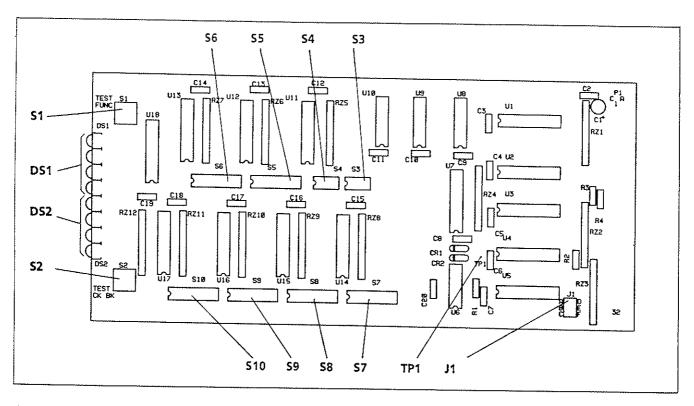

| 3.3. JUMPER AND SWITCH SETTINGS'                                                                                                                                                                                                                                             | 3-11        | 10.3.6. Latches                                                                                                                                                                                                                                                 | 10-3            |

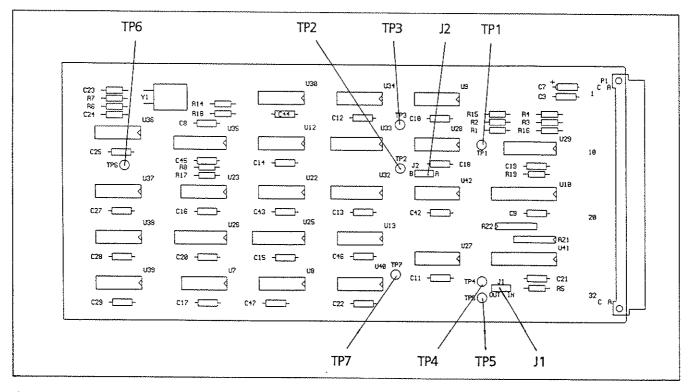

| 3.3.1. RFL 97 TX INTER Module                                                                                                                                                                                                                                                | 3-11        | 10.3.7. Microprocessor Supervisor                                                                                                                                                                                                                               | 10-3            |

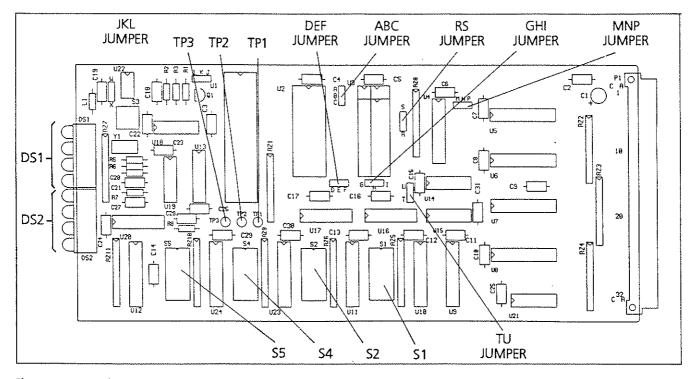

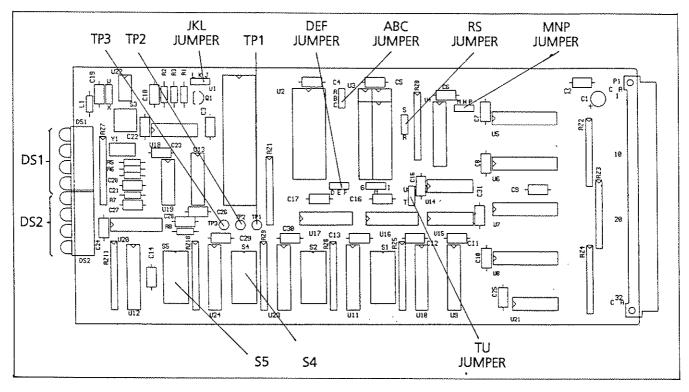

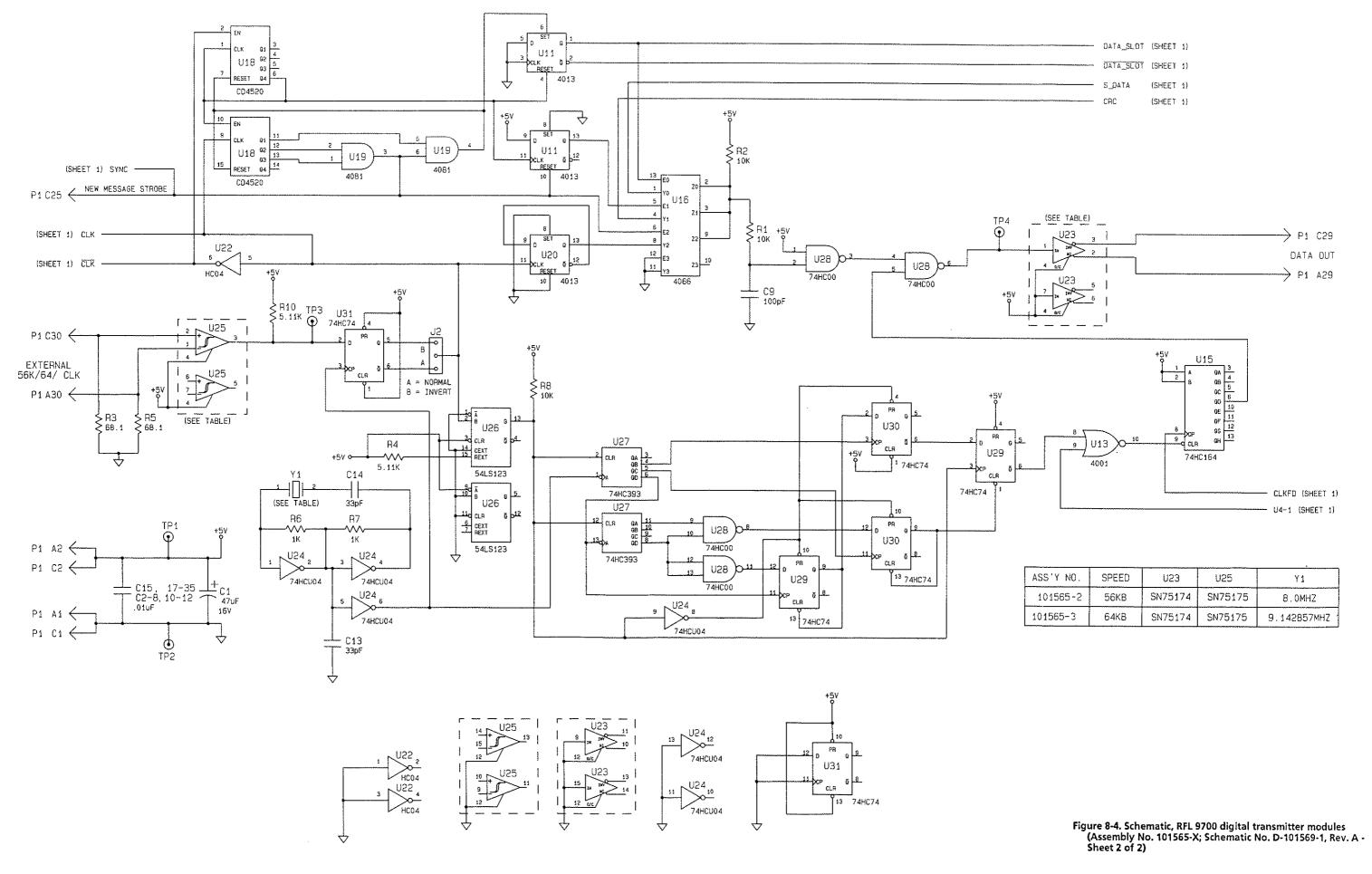

| 3.3.2. Digital Transmitter Module                                                                                                                                                                                                                                            | 3-14        | 10.3.8. Watchdog Timer                                                                                                                                                                                                                                          | 10-4            |

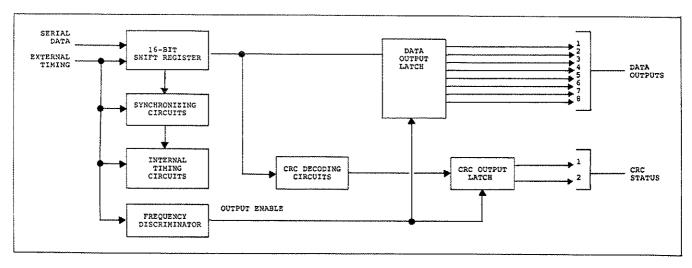

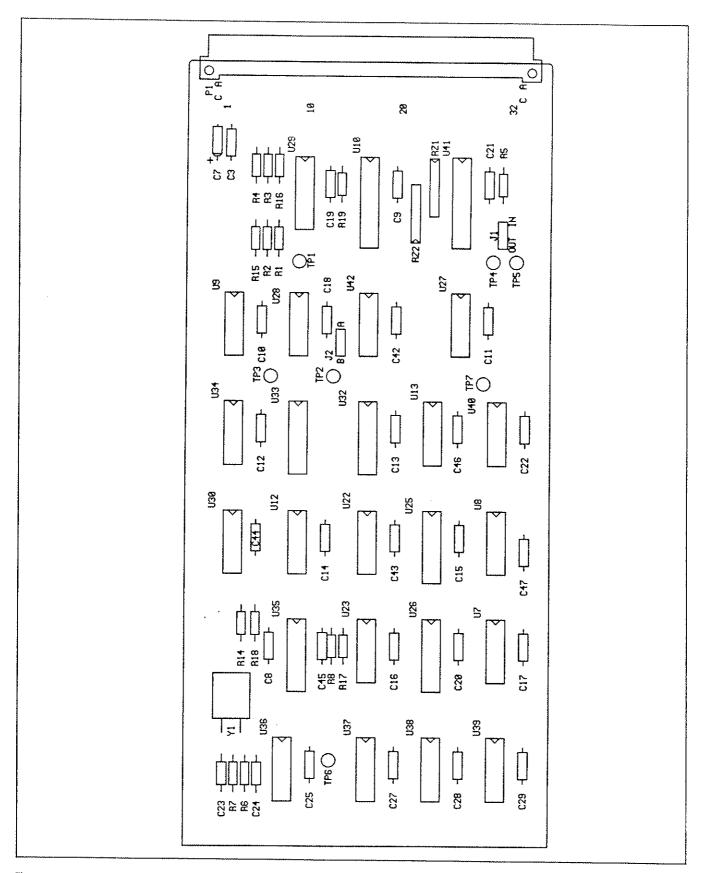

| 3.3.3. Digital Receiver Modules                                                                                                                                                                                                                                              | 3-14        | 10.3.9. Output Ports                                                                                                                                                                                                                                            | 10-4            |

| 3.3.4. CPU Modules                                                                                                                                                                                                                                                           | 3-14        | 10.3.8. Watchdog Timer                                                                                                                                                                                                                                          | 10-4            |

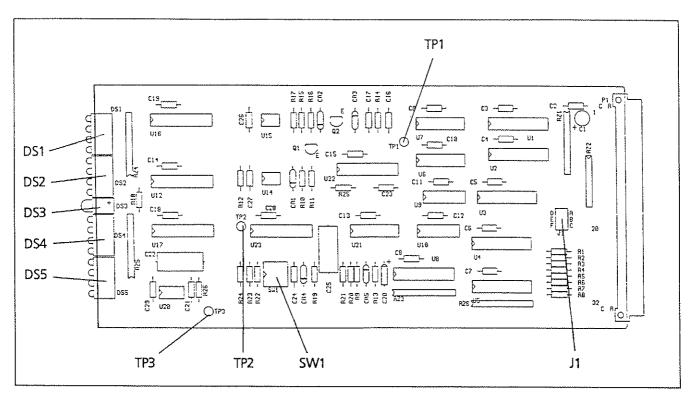

| 3.3.5. RFL 97 IND/OUT Module                                                                                                                                                                                                                                                 | 3-15        | 10.4.1. Program Structure                                                                                                                                                                                                                                       | 10-4            |

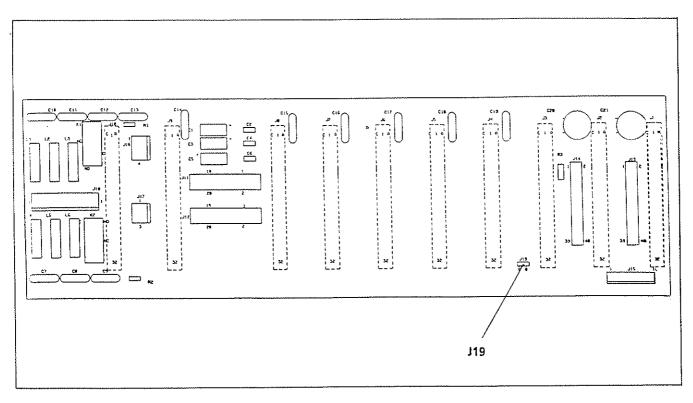

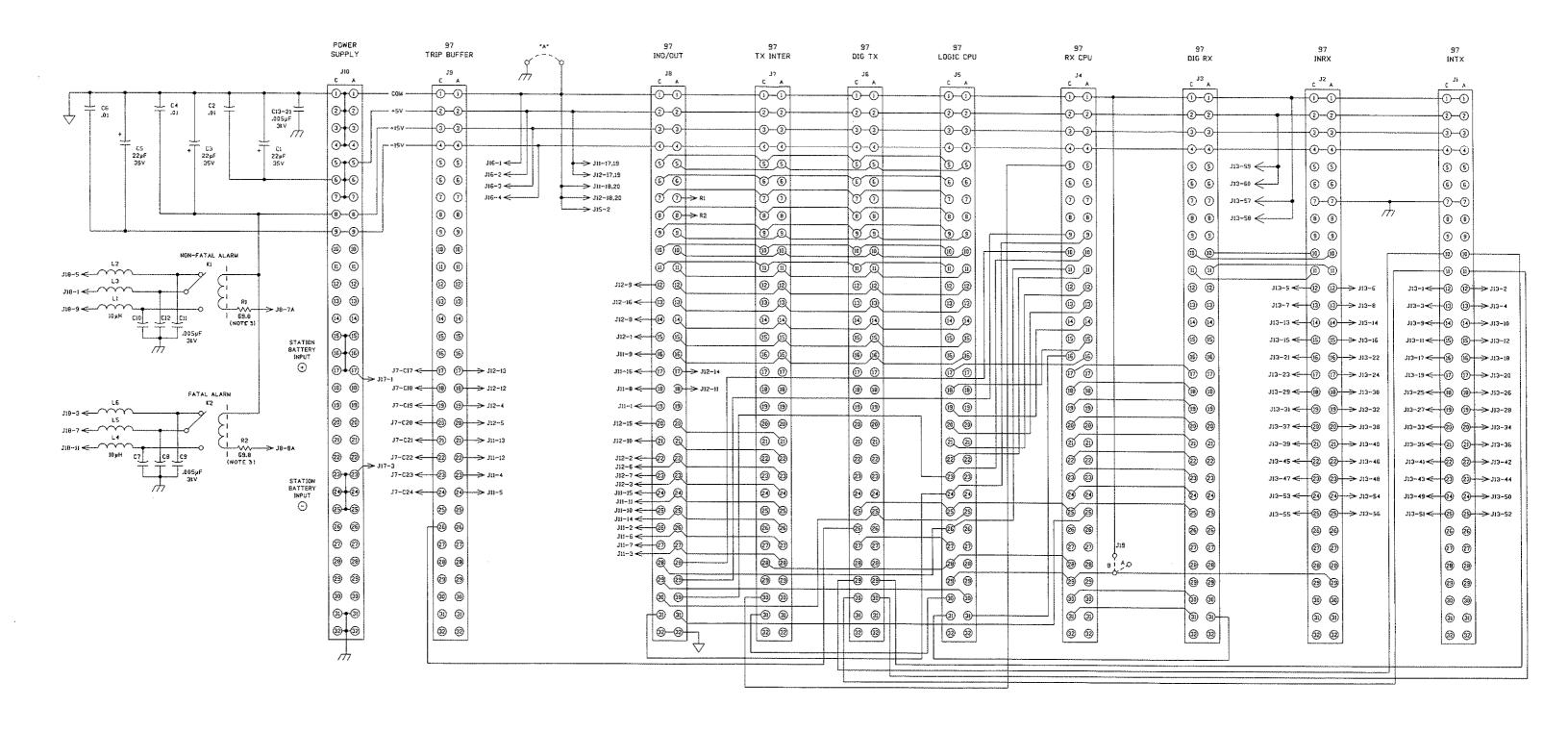

| 3.3.6. RFL 97A INTER Chassis Motherboard .                                                                                                                                                                                                                                   | 3-16        | 10.4.2. Initialization Block                                                                                                                                                                                                                                    | 10-5            |

|                                                                                                                                                                                                                                                                              | 3-10        |                                                                                                                                                                                                                                                                 |                 |

| 3.4. INITIAL STARTUP AND                                                                                                                                                                                                                                                     | 2 - 6       | 10.4.3. Primary Input Data Block                                                                                                                                                                                                                                | 10-6            |

| SYSTEM VERIFICATION PROCEDURES                                                                                                                                                                                                                                               | 3-16        | 10.4.4. Primary Input Data Processing Block                                                                                                                                                                                                                     | 10-6            |

| 3.4.1. Equipment Requirements                                                                                                                                                                                                                                                | 3-16        | 10.4.5. Secondary Input Data Block                                                                                                                                                                                                                              | 10-9            |

| 3.4.2. Power Supply Output Verification .                                                                                                                                                                                                                                    | 3-16        | 10.4.6. Output Data Block                                                                                                                                                                                                                                       | 10-9            |

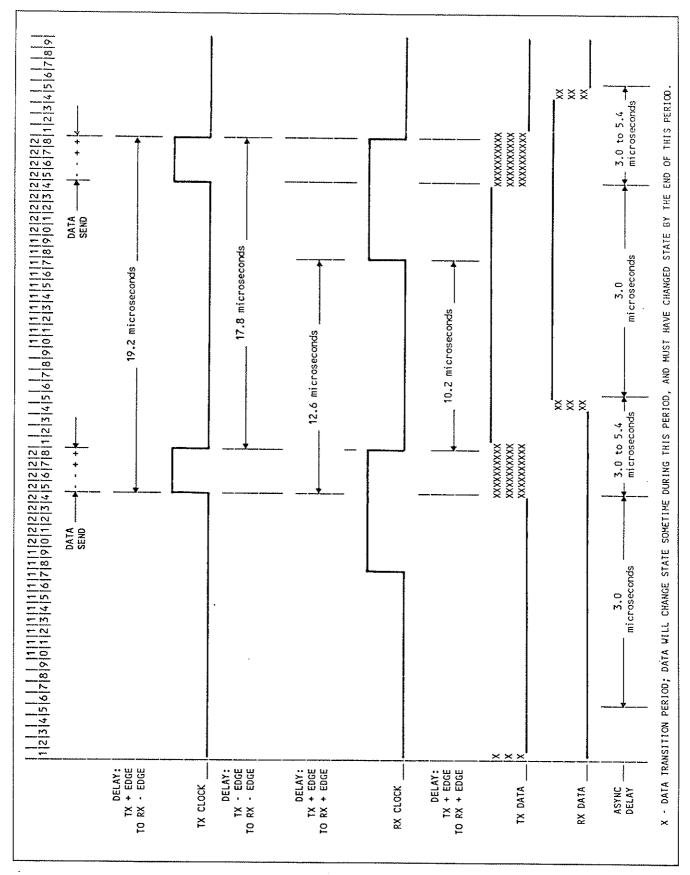

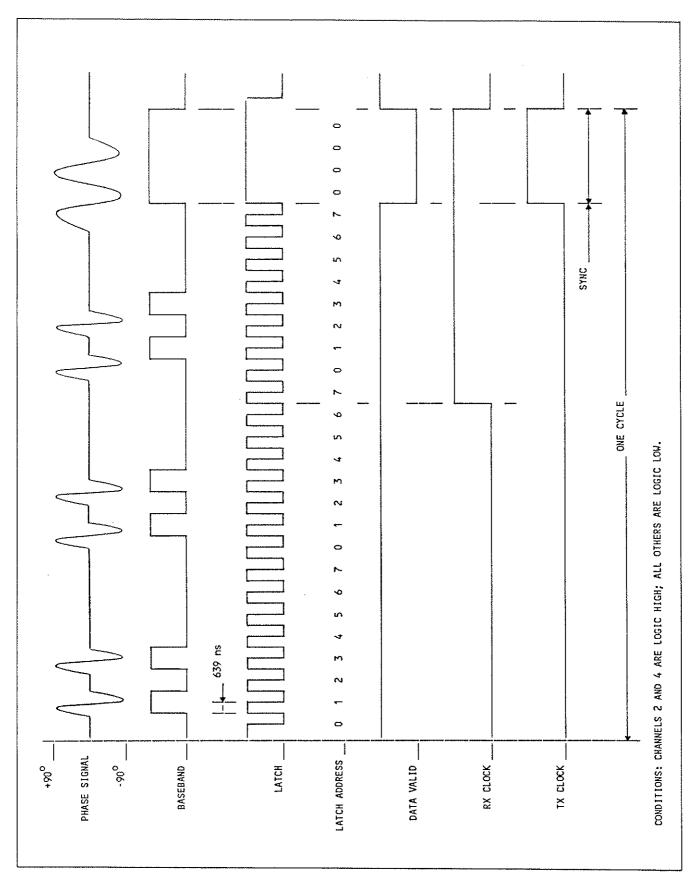

| 3.4.3. Communications Link Verification .                                                                                                                                                                                                                                    | 3-17        |                                                                                                                                                                                                                                                                 |                 |

| 3.4.4. Verification Procedures                                                                                                                                                                                                                                               | 3-19        |                                                                                                                                                                                                                                                                 |                 |

| 3.4.5. Fiber Optic Signal Level                                                                                                                                                                                                                                              |             |                                                                                                                                                                                                                                                                 |                 |

| Verification                                                                                                                                                                                                                                                                 | 3-21        |                                                                                                                                                                                                                                                                 |                 |

| 3.4.6. RS-449 Or X.21 Signal Verification                                                                                                                                                                                                                                    | 3-23        |                                                                                                                                                                                                                                                                 |                 |

| DE CYCTEM OREDATION                                                                                                                                                                                                                                                          | 3.72        |                                                                                                                                                                                                                                                                 |                 |

### **TABLE OF CONTENTS - continued.**

| Section 11. LOGIC CPU MODULE  11.1. DESCRIPTION  11.2. SPECIFICATIONS  11.3. HARDWARE DESCRIPTION  11.3.1. Program Storage EPROM  11.3.2. Static RAM  11.3.3. Microprocessor                                                     |       | Section 15. FIBER OPTIC HEADS  15.1. INTRODUCTION  15.2. FIBER OPTIC EMITTER HEADS                                                                                                                                                                                                                                                                                                      |       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

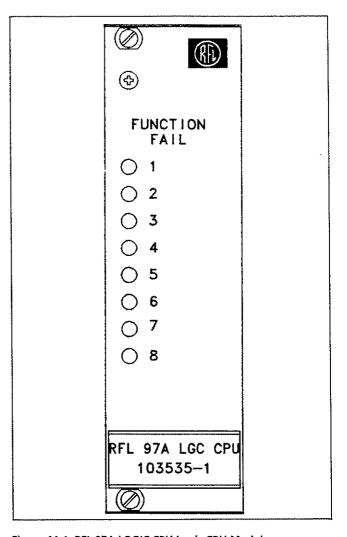

| 11.1. DESCRIPTION                                                                                                                                                                                                                | 11-1  | 15.1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                       | 15-1  |

| 11.2. SPECIFICATIONS                                                                                                                                                                                                             | 11-1  | 15.2 FIRER OPTIC EMITTER HEADS                                                                                                                                                                                                                                                                                                                                                          | 15-1  |

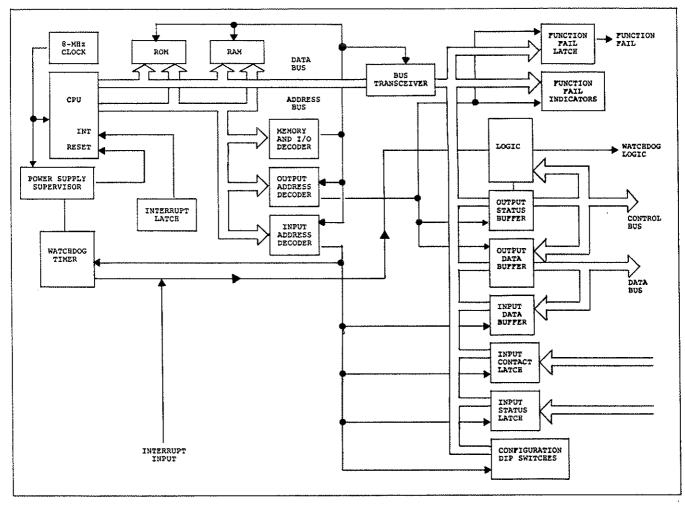

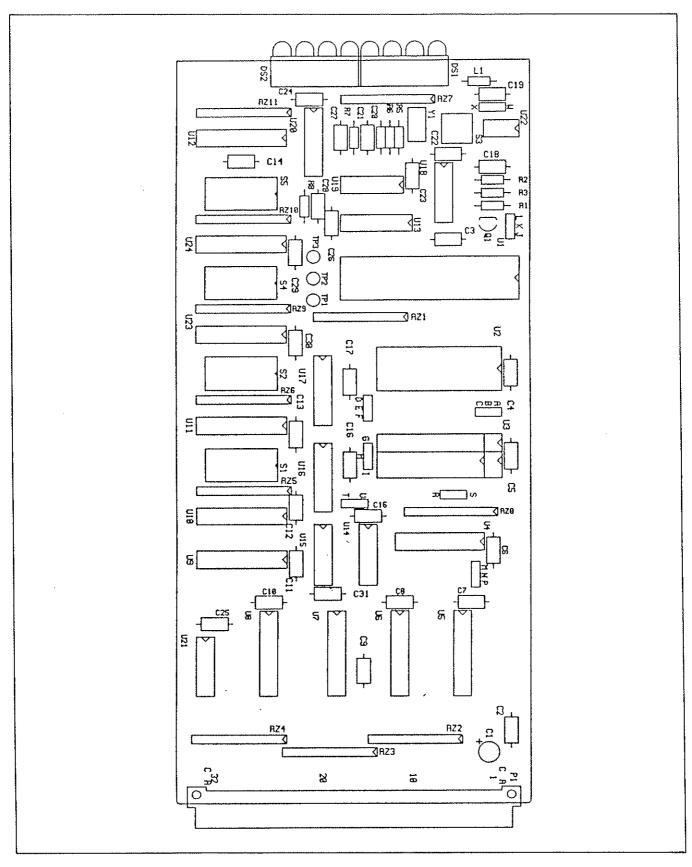

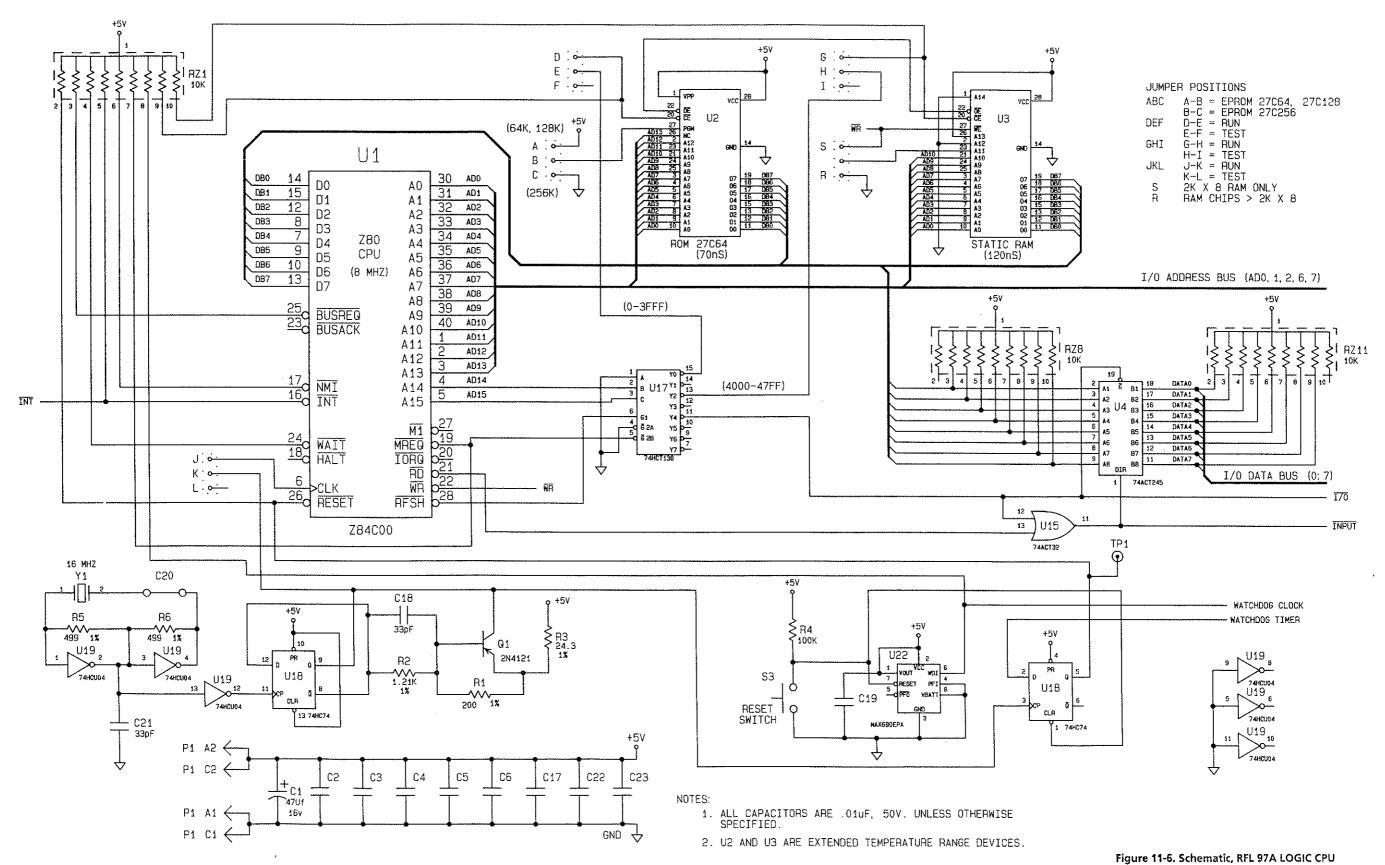

| 11.3. HARDWARE DESCRIPTION                                                                                                                                                                                                       | 11-1  | 15.2.1 Description                                                                                                                                                                                                                                                                                                                                                                      | 15-1  |

| 11.3.1. Program Storage EPROM                                                                                                                                                                                                    | 11-2  | 15.2.1. Description                                                                                                                                                                                                                                                                                                                                                                     | 10-1  |

| 11 3 2 Static RAM                                                                                                                                                                                                                | 1172  | 15.2. FIBER OPTIC EMITTER HEADS  15.2.1. Description  15.2.2. Specifications  15.2.3. Theory Of Operation  15.2.3.1. RFL 97 FO TX-8M 850-nm  Multimode Fiber Optic Emitter Head  15.2.3.2. RFL 97 FO TX-13M And  RFL 97 FO TX-13S 1300-nm  Fiber Optic Emitter Heads  15.2.3.3. RFL 97 FO TX-13LS 1300-nm  Singlemode Laser Fiber Optic  Emitter Head  15.3. FIBER OPTIC DETECTOR HEADS | 15-1  |

| 11 3 3 Microprocessor                                                                                                                                                                                                            | 117   | 15.2.5. meory of Operation                                                                                                                                                                                                                                                                                                                                                              | 15-2  |

| 11.3.4 Address Decoding                                                                                                                                                                                                          | 11-2  | 15.2.3.1. RFL 97 FO TX-8M 850-nm                                                                                                                                                                                                                                                                                                                                                        |       |

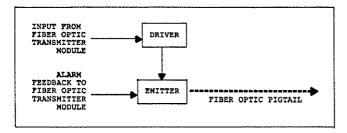

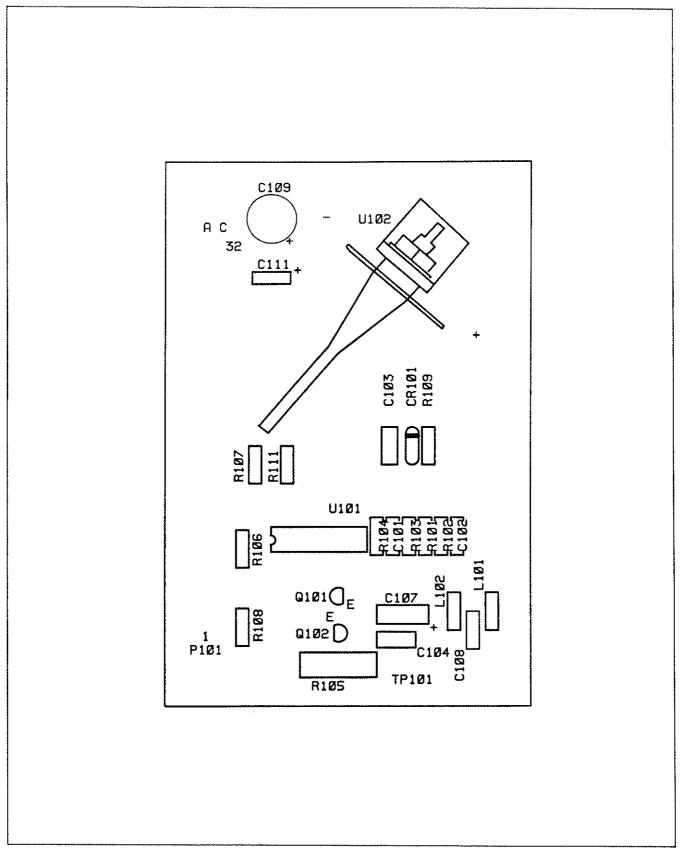

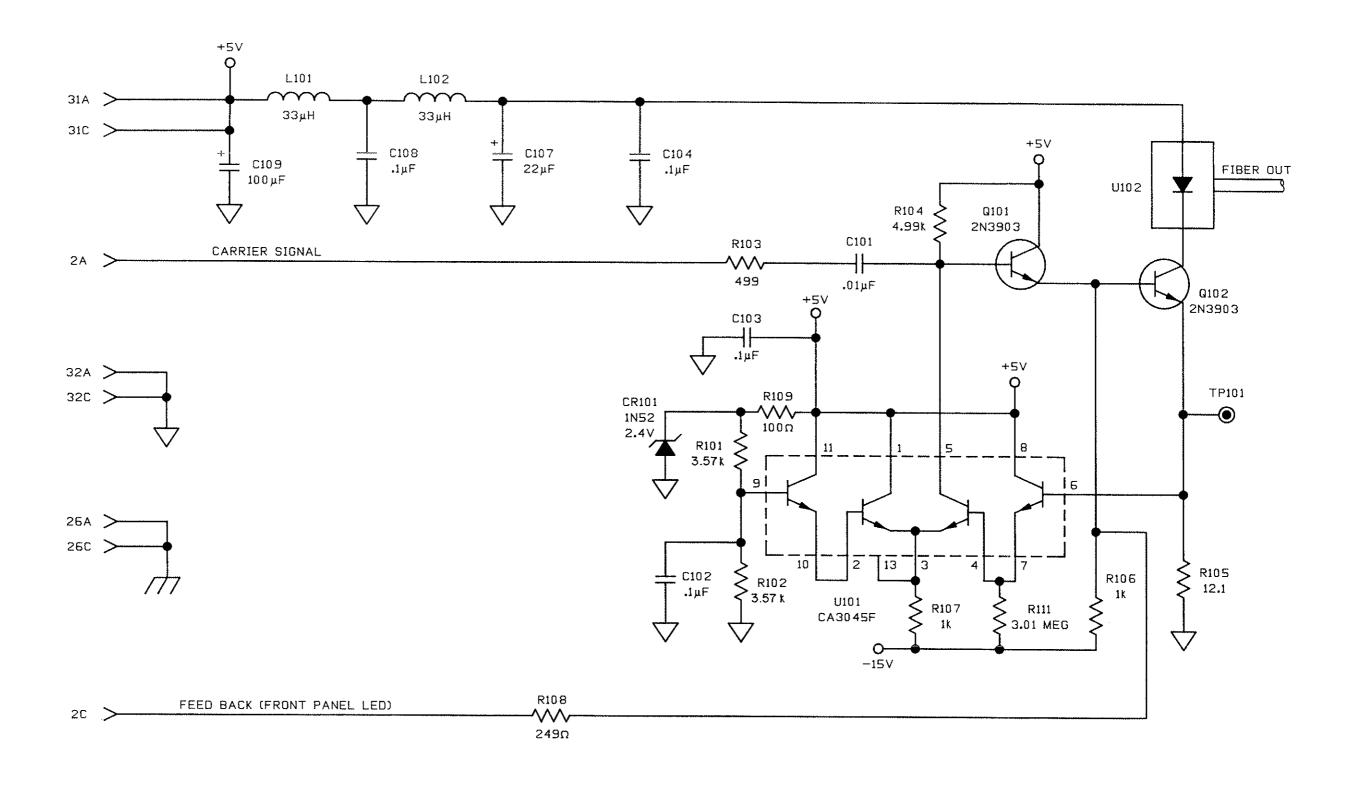

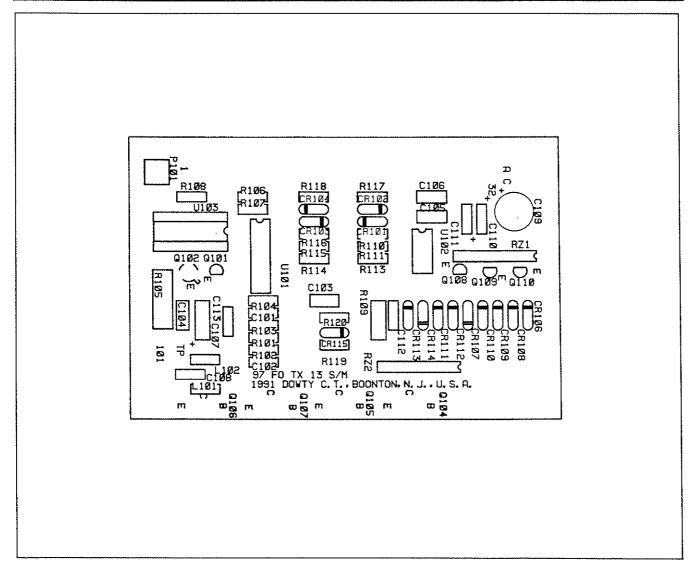

| 11.3.5 Input Ports                                                                                                                                                                                                               | 11-3  | Multimode Fiber Optic Emitter Head                                                                                                                                                                                                                                                                                                                                                      | 15-2  |

| 11.3.6 Latchor                                                                                                                                                                                                                   | 11-3  | 15.2.3.2. RFL 97 FO TX-13M And                                                                                                                                                                                                                                                                                                                                                          |       |

| 11.2.7 Microprocessor Companies                                                                                                                                                                                                  | (1~3  | RFL 97 FO TX-135 1300-nm                                                                                                                                                                                                                                                                                                                                                                |       |

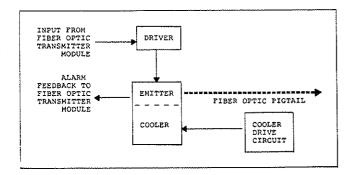

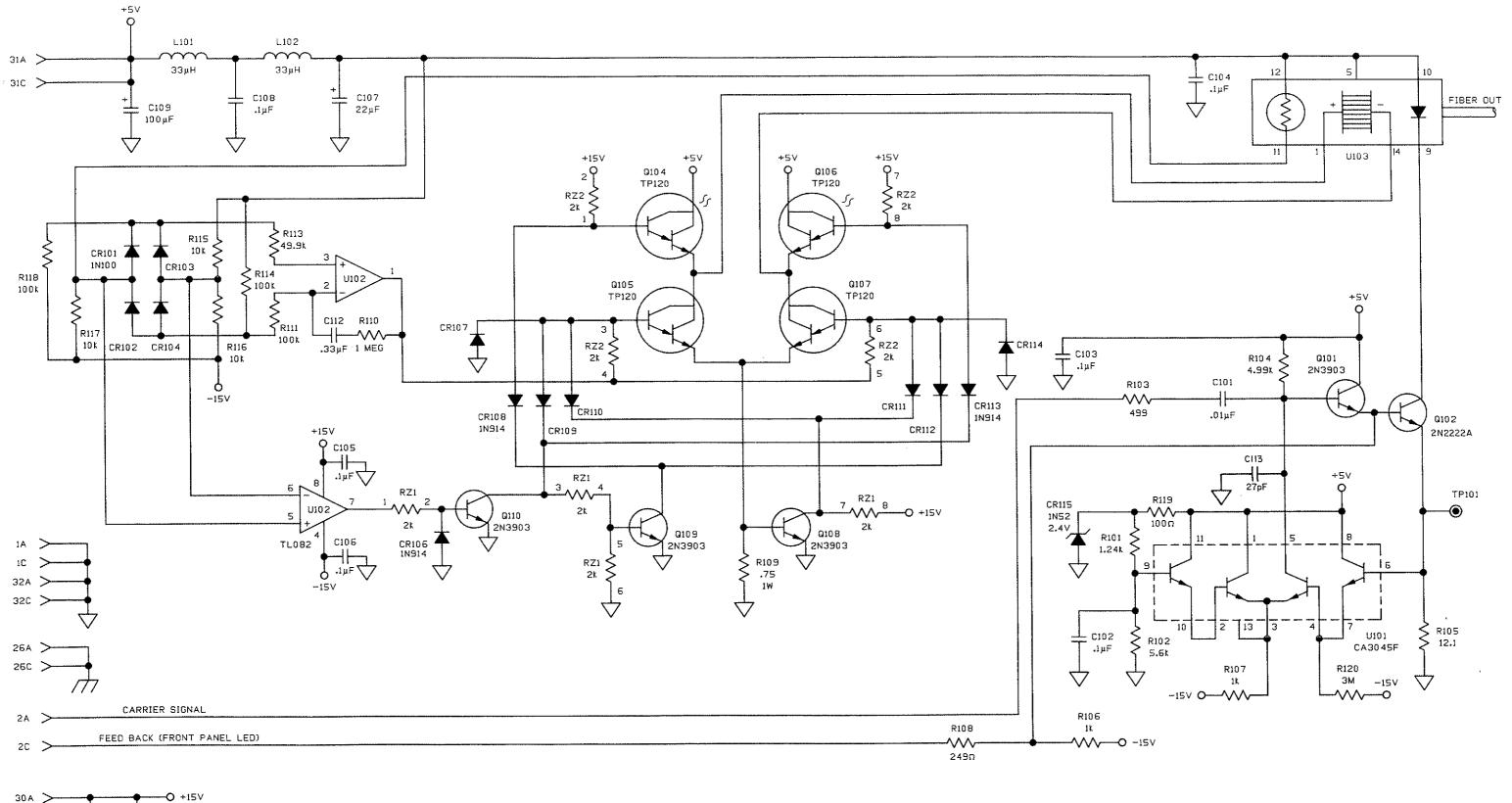

| 11.3.4. Address Decoding 11.3.5. Input Ports 11.3.6. Latches 11.3.7. Microprocessor Supervisor 11.3.8. Watchdog Timer                                                                                                            | 11-4  | Fiber Optic Emitter Heads .                                                                                                                                                                                                                                                                                                                                                             | 15-2  |

| 11.3.6. Watchdog timer                                                                                                                                                                                                           | 11-4  | 15.2.3.3. RFL 97 FO TX-13LS 1300-nm                                                                                                                                                                                                                                                                                                                                                     |       |

| 11.3.9. Output Ports                                                                                                                                                                                                             | 11-4  | Singlemode Laser Fiber Optic                                                                                                                                                                                                                                                                                                                                                            |       |

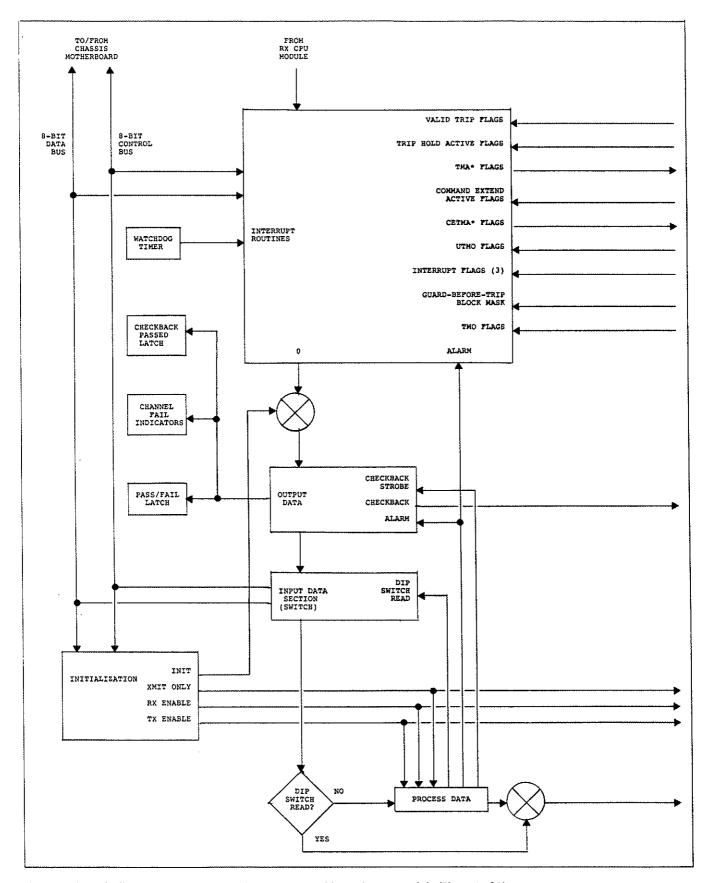

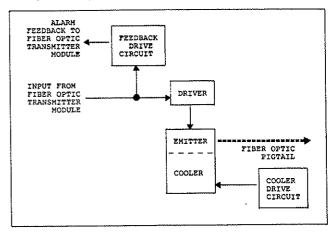

| 11.4. SOFTWARE DESCRIPTION .<br>11.4.1. Program Structure                                                                                                                                                                        | 11-5  | Emitter Head                                                                                                                                                                                                                                                                                                                                                                            | 15-3  |

| 11.4.1. Program Structure                                                                                                                                                                                                        | 11-5  | 15.3. FIBER OPTIC DETECTOR HEADS                                                                                                                                                                                                                                                                                                                                                        | 15-17 |

| 11.4.2. The Background Program                                                                                                                                                                                                   | 11-5  | 15.3.1. Description                                                                                                                                                                                                                                                                                                                                                                     | 15-17 |

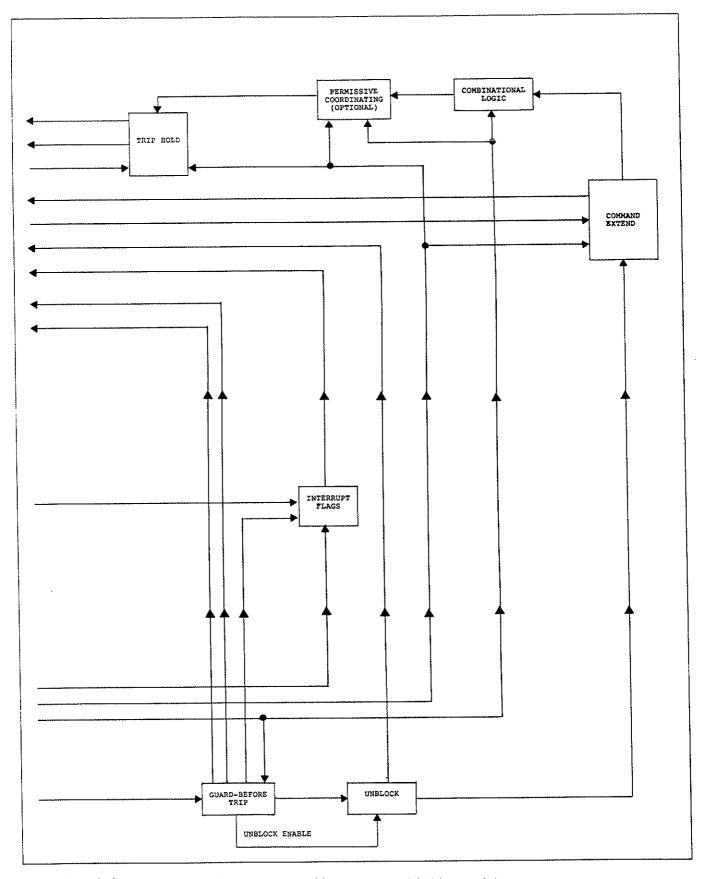

| 11.4.3. Interrupt Routines 11.4.4. Initialization Program Block 11.4.5. Input/Output Program Block                                                                                                                               | 11-5  | 15.3.1. Description 15.3.2. Specifications 15.3.3. Theory Of Operation                                                                                                                                                                                                                                                                                                                  | 15-17 |

| 11.4.4. Initialization Program Block                                                                                                                                                                                             | 11-10 | 15.3.3. Theory Of Operation                                                                                                                                                                                                                                                                                                                                                             | 15-17 |

| 11.4.5. Input/Output Program Block                                                                                                                                                                                               | 11-11 | 15.3.3.1. RFL 97 FO RX-8M 850-nm                                                                                                                                                                                                                                                                                                                                                        |       |

| 11.4.6. Input Data Processing Program Block<br>11.4.7. Guard-Before-Trip Program Block                                                                                                                                           | 11-12 | Fiber Optic Detector Head .                                                                                                                                                                                                                                                                                                                                                             | 15-18 |

| 11.4.7. Guard-Before-Trip Program Block                                                                                                                                                                                          | 11-13 | 15.3.3.2. RFL 97 FO RX-13M And                                                                                                                                                                                                                                                                                                                                                          |       |

| 11.4.8. Unblock Program Block                                                                                                                                                                                                    | 11-14 | RFL 97 FO RX-13/15S Fiber Optic                                                                                                                                                                                                                                                                                                                                                         |       |

| 11.4.9. Command Extend Program Block                                                                                                                                                                                             | 11-14 | Singlemode Laser Fiber Optic Emitter Head  15.3. FIBER OPTIC DETECTOR HEADS  15.3.1. Description  15.3.2. Specifications  15.3.3. Theory Of Operation  15.3.3.1. RFL 97 FO RX-8M 850-nm Fiber Optic Detector Head  15.3.3.2. RFL 97 FO RX-13M And RFL 97 FO RX-13/1SS Fiber Optic Detector Heads                                                                                        | 15-18 |

| 11.4.10. Combinational Logic Program Block                                                                                                                                                                                       | 11-14 |                                                                                                                                                                                                                                                                                                                                                                                         | 15-10 |

| 11.4.11. Trip Hold Program Block                                                                                                                                                                                                 | 11-15 | Section 16 POWER CLIRRIES                                                                                                                                                                                                                                                                                                                                                               |       |

| 11.4.12. Permissive Coordinating                                                                                                                                                                                                 |       | 16.1 DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                        | 16 1  |

| Software Option                                                                                                                                                                                                                  | 11-15 | 16.1. DESCRIPTION 16.2. SPECIFICATIONS 16.3. THEORY OF OPERATION 16.3.1. Input Protection Circuits                                                                                                                                                                                                                                                                                      | 10-1  |

|                                                                                                                                                                                                                                  |       | 16.3 THEORY OF ODERATION                                                                                                                                                                                                                                                                                                                                                                | 10-1  |

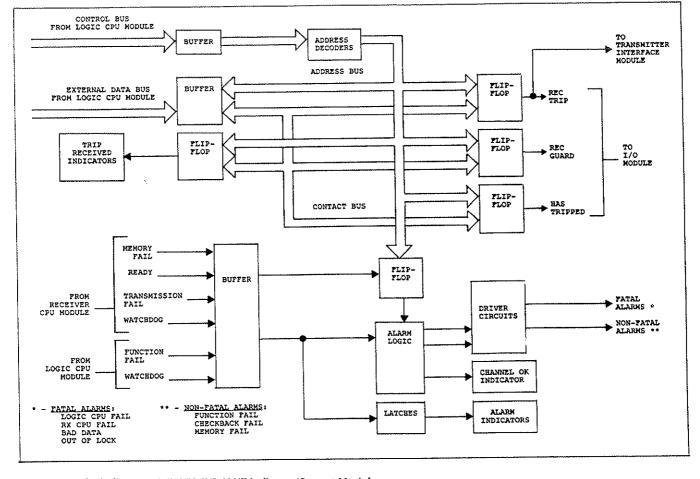

| Section 12. INDICATOR/OUTPUT MODULE                                                                                                                                                                                              |       | 16.2.1 input Protection Circuits                                                                                                                                                                                                                                                                                                                                                        | 10-2  |

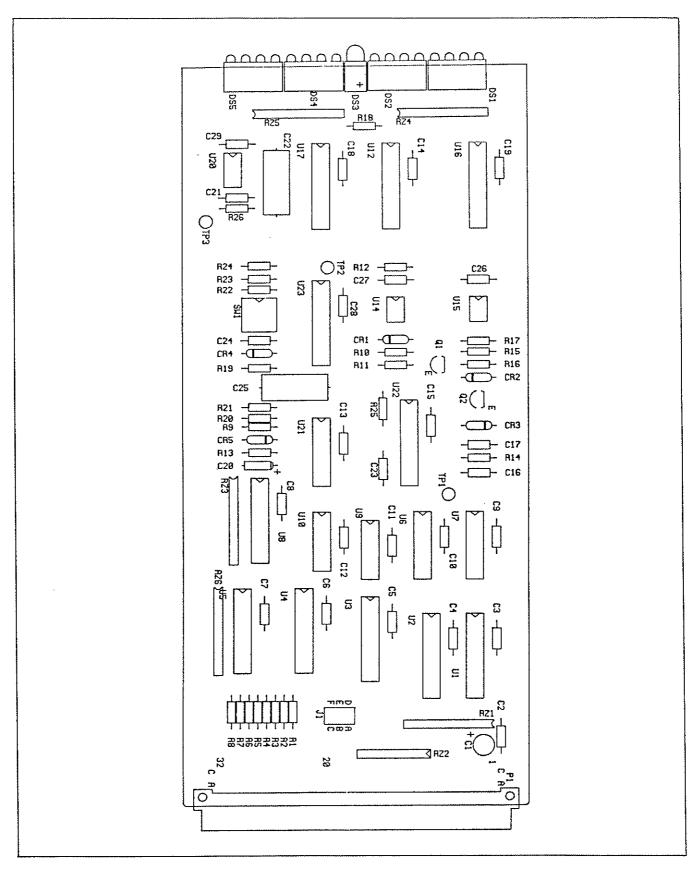

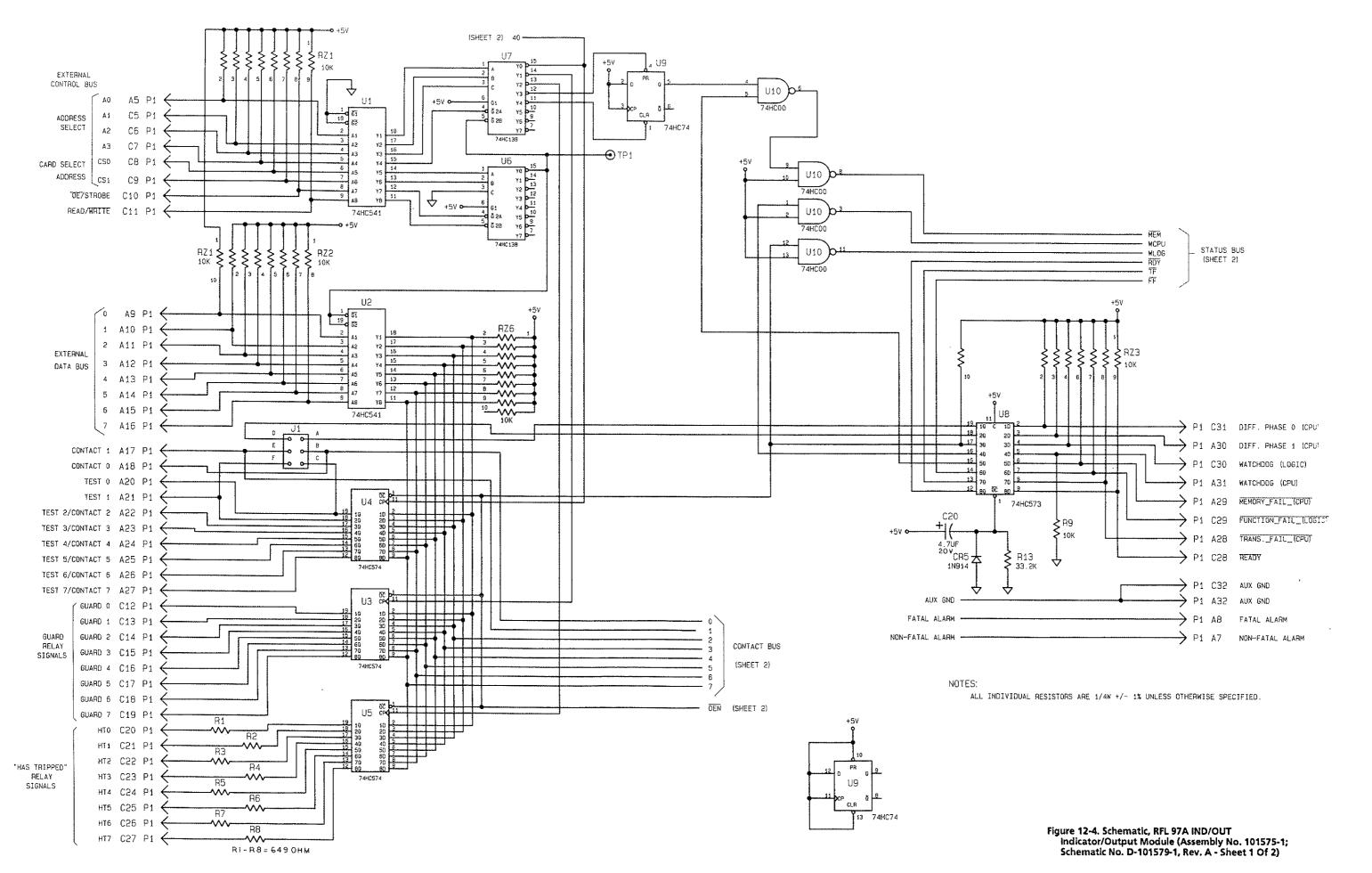

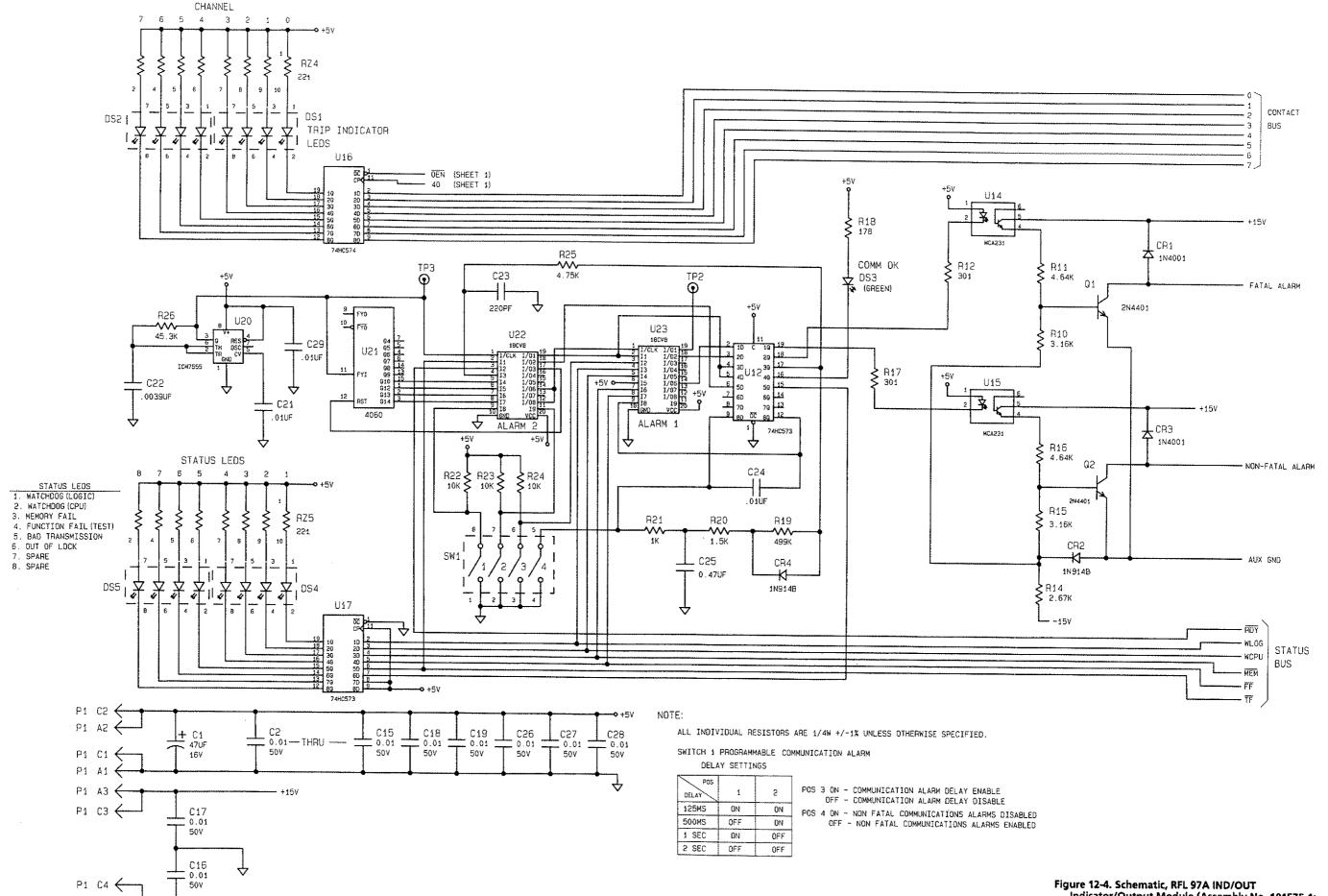

| 12.1. DESCRIPTION                                                                                                                                                                                                                | 17-1  | 16.3.2 Input Converter                                                                                                                                                                                                                                                                                                                                                                  | 10-2  |

| 12.2. SPECIFICATIONS                                                                                                                                                                                                             | 12-1  | 16.3.2. input Converter .                                                                                                                                                                                                                                                                                                                                                               | 16-3  |

| 12.3 THEORY OF OPERATION                                                                                                                                                                                                         | 12-1  | 16.3.4. 45 Volt Dode Converter                                                                                                                                                                                                                                                                                                                                                          | 16-3  |

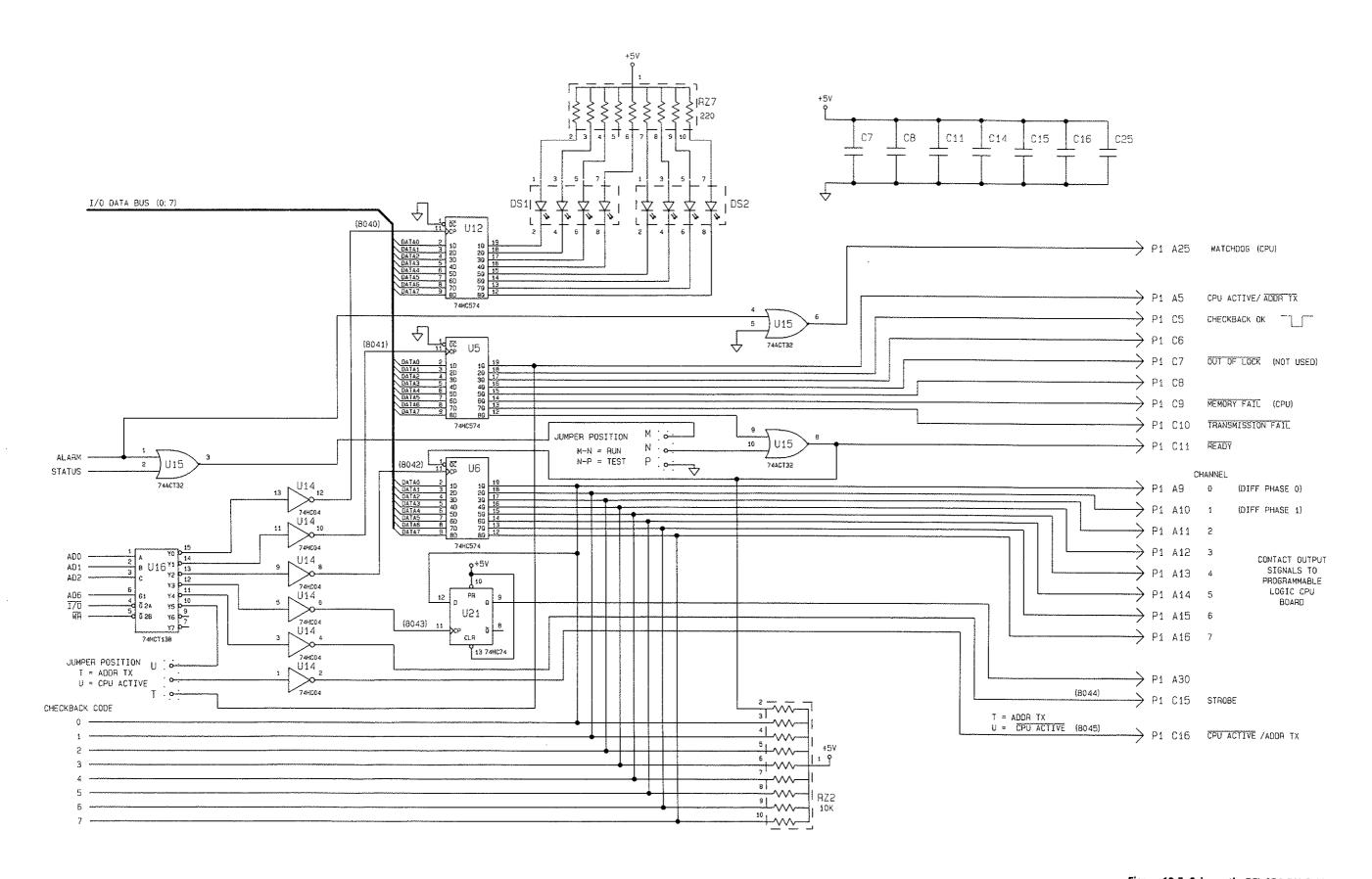

| 12.3.1 Address Decoders                                                                                                                                                                                                          | 127   | 16.3.2. Input Converter 16.3.3. +5-Volt Dc/dc Converter 16.3.415-Volt Dc/dc Converter 16.3.5. Thermal And Overvoltage Protection                                                                                                                                                                                                                                                        | 16-3  |

| 12.3.2. Output Interface                                                                                                                                                                                                         | 12-2  | 16.3.5. Thermal And Overvoltage Protection                                                                                                                                                                                                                                                                                                                                              | 16-4  |

| Section 12. INDICATOR/OUTPUT MODULE 12.1. DESCRIPTION 12.2. SPECIFICATIONS 12.3. THEORY OF OPERATION 12.3.1. Address Decoders 12.3.2. Output Interface 12.3.3. Alarm Decoder Circuits 12.3.4. Communications Alarm Delay Circuit | 12-2  |                                                                                                                                                                                                                                                                                                                                                                                         |       |

| 12.3.4. Communications Alarm Dalay Circuit                                                                                                                                                                                       | 12-2  | Section 17. CHASSIS 17.1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                  |       |

| 12.3.5. Alarm Relay Drive Circuits                                                                                                                                                                                               | 12-2  | 17.1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                      | 17-1  |

| i filosos Aldisii Nelay Dilye Circuis                                                                                                                                                                                            | 1 Z-4 | 17.2. RFL 97 CHAS SINGLE-EURO CHASSIS                                                                                                                                                                                                                                                                                                                                                   | 17-1  |

| 12.3.6. Indicator Drive Circuits                                                                                                                                                                                                 | 12-4  | 17.3. RFL 97 INTER INTERCONNECT                                                                                                                                                                                                                                                                                                                                                         |       |

| 12.3.7. Power-On Reset Circuit                                                                                                                                                                                                   | 12-4  | MOTHERBOARD                                                                                                                                                                                                                                                                                                                                                                             | 17-1  |

| Castion 43 PIRCH ORTIGEMENT AND                                                                                                                                                              |       | 17.4. RFL 97 449 INTER                                                                                                                                                                                                                                                                                                                                                                  |       |

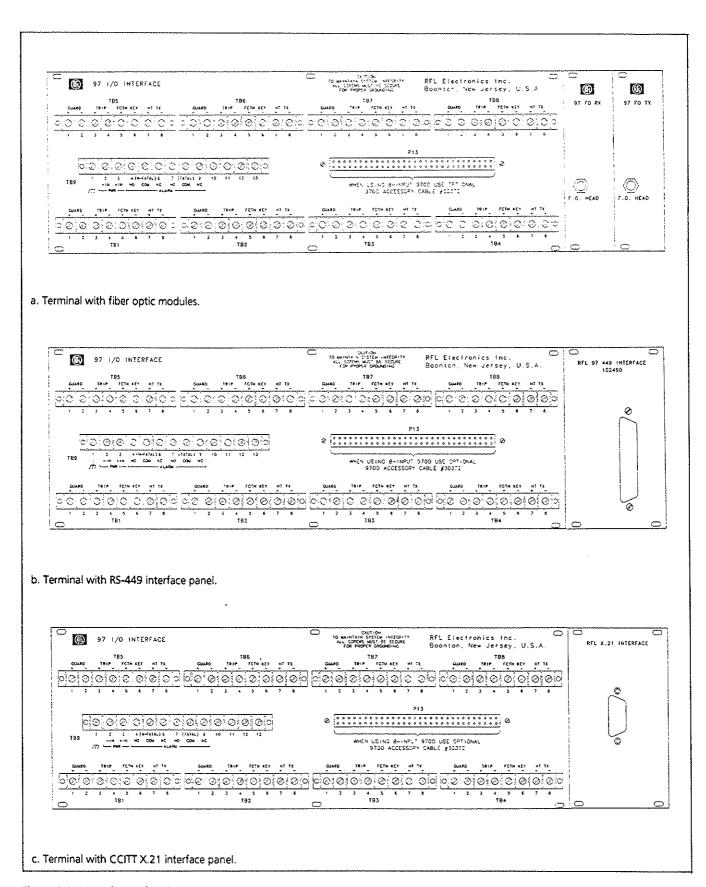

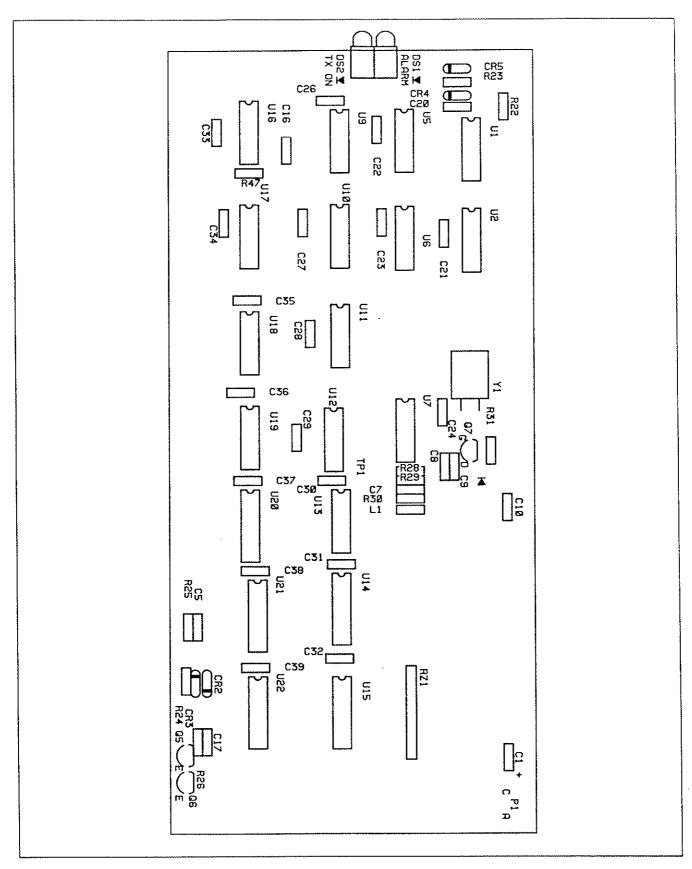

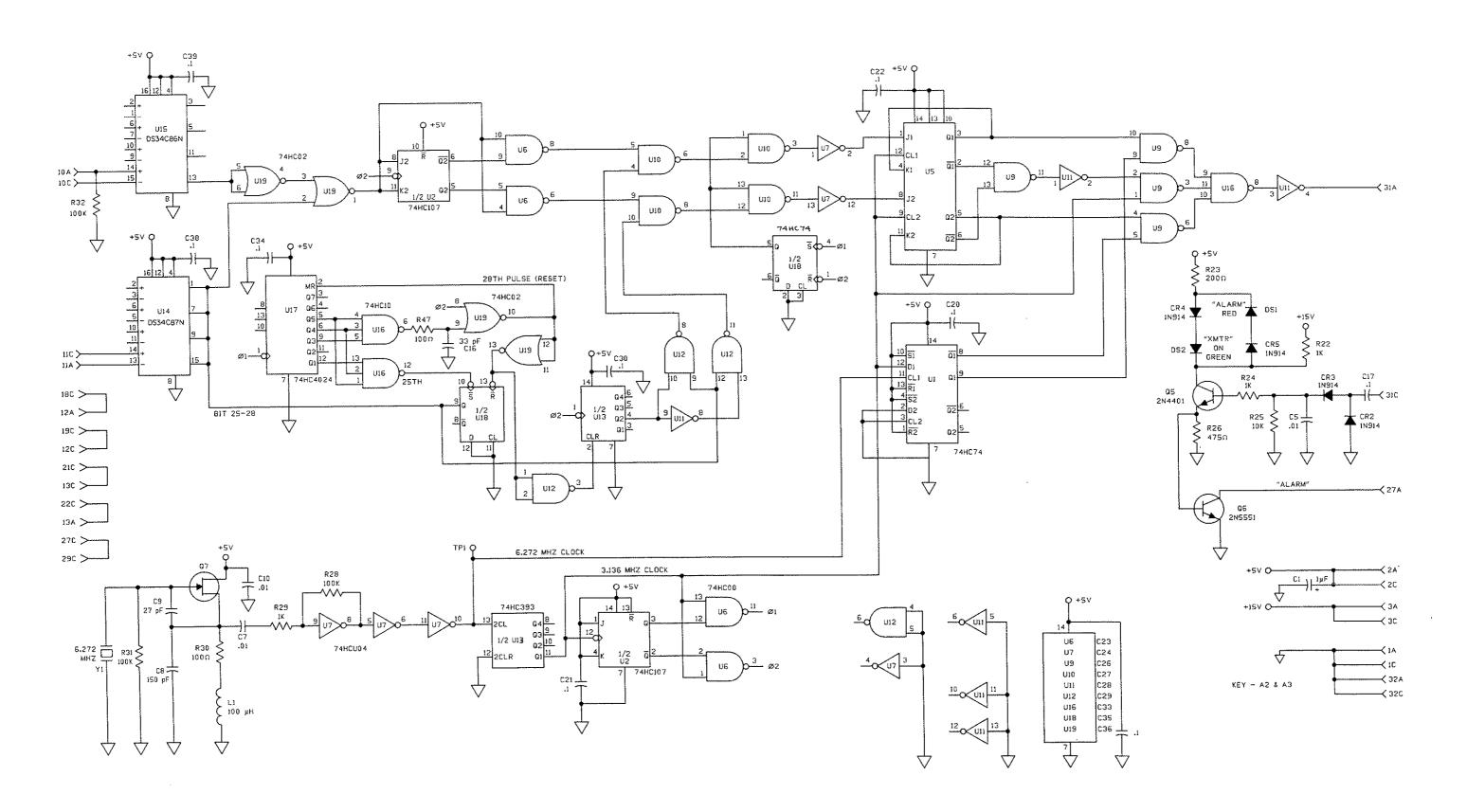

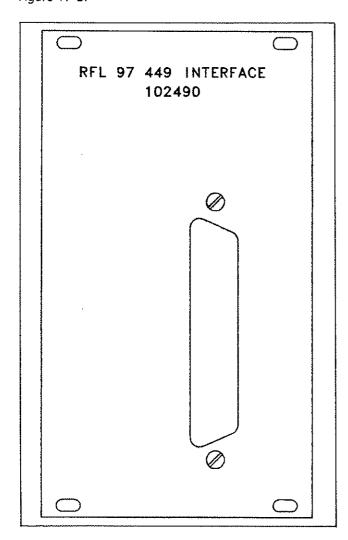

| Section 13. FIBER OPTIC TRANSMITTER MODULES                                                                                                                                                                                      |       | RS-449 INTERFACE PANEL                                                                                                                                                                                                                                                                                                                                                                  | 17-5  |

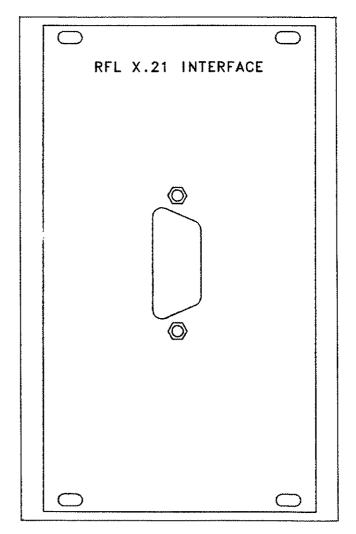

| 13.1. DESCRIPTION                                                                                                                                                                                                                | 13-1  | 17.5. RFL 97 X.21 INTER                                                                                                                                                                                                                                                                                                                                                                 |       |

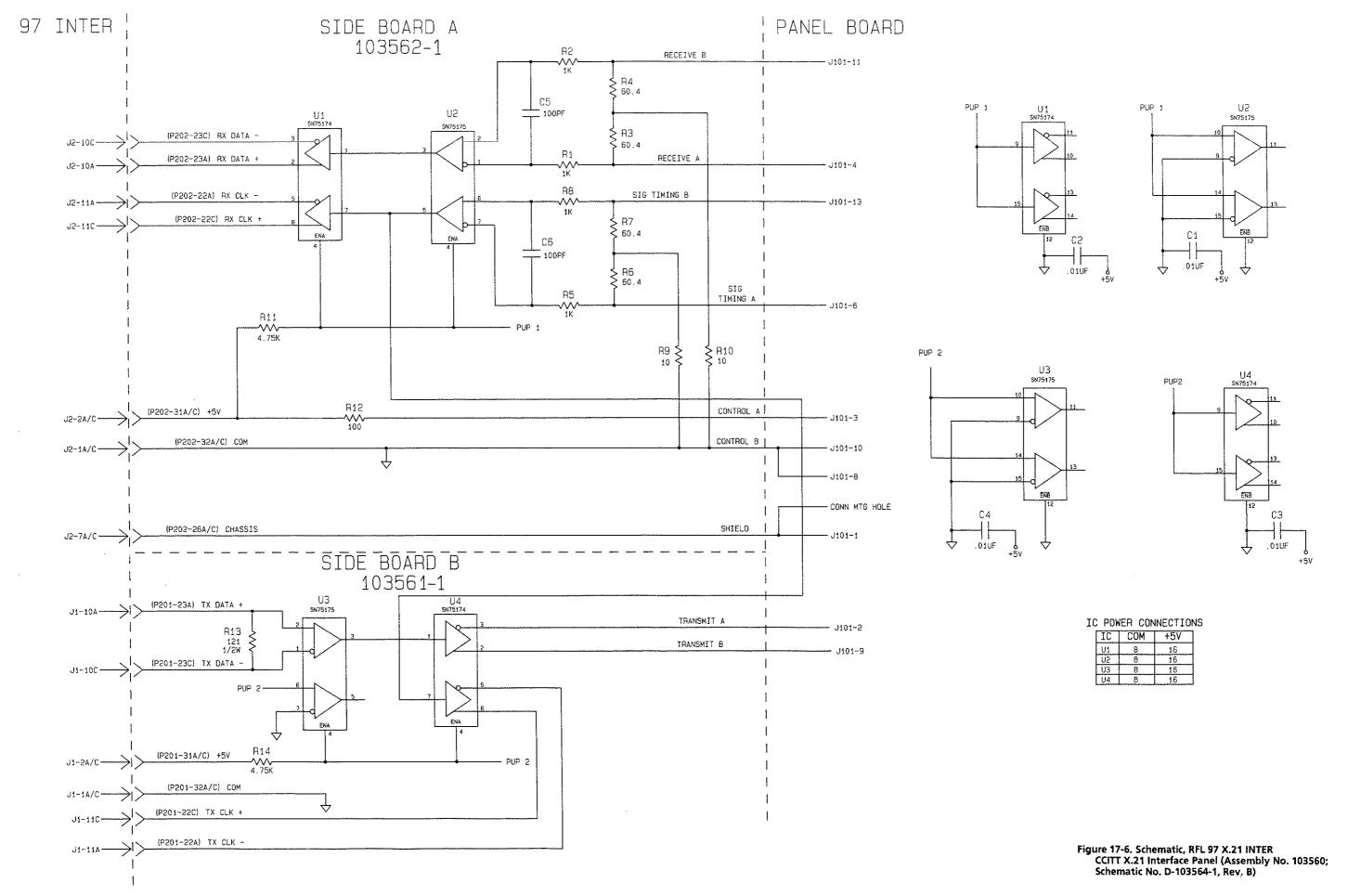

| 13.2. SPECIFICATIONS                                                                                                                                                                                                             | 13-1  | CCITT X.21 INTERFACE PANEL                                                                                                                                                                                                                                                                                                                                                              | 17-5  |

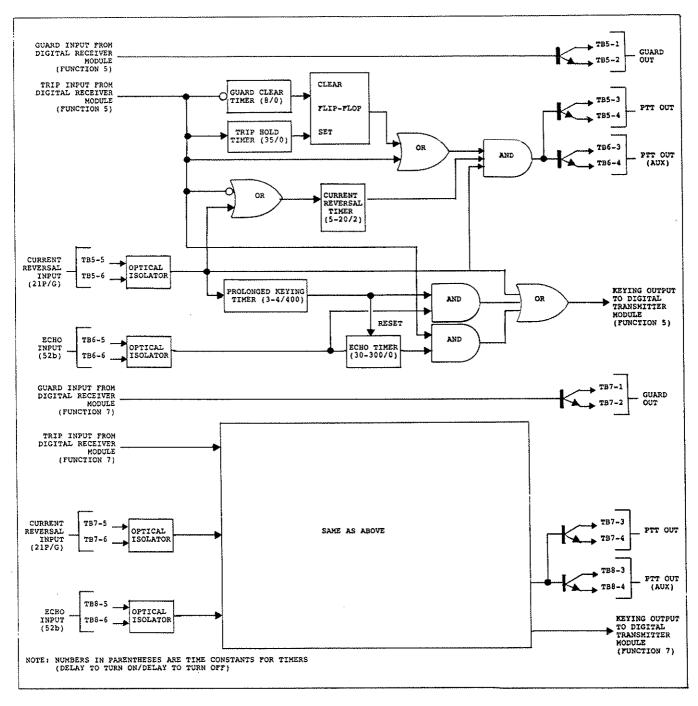

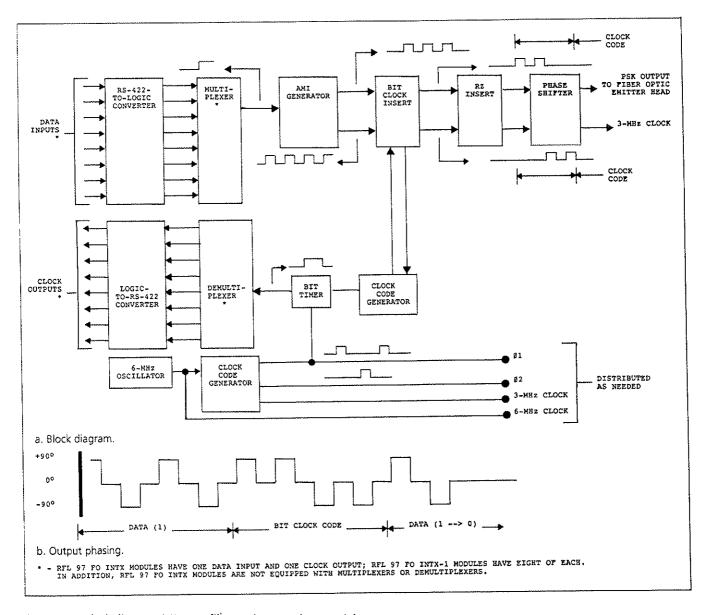

| 13.1. DESCRIPTION 13.2. SPECIFICATIONS 13.3. THEORY OF OPERATION                                                                                                                                                                 | 13-2  |                                                                                                                                                                                                                                                                                                                                                                                         |       |

|                                                                                                                                                                                                                                  |       | Section 18. ACCESSORY EQUIPMENT 18.1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                      |       |

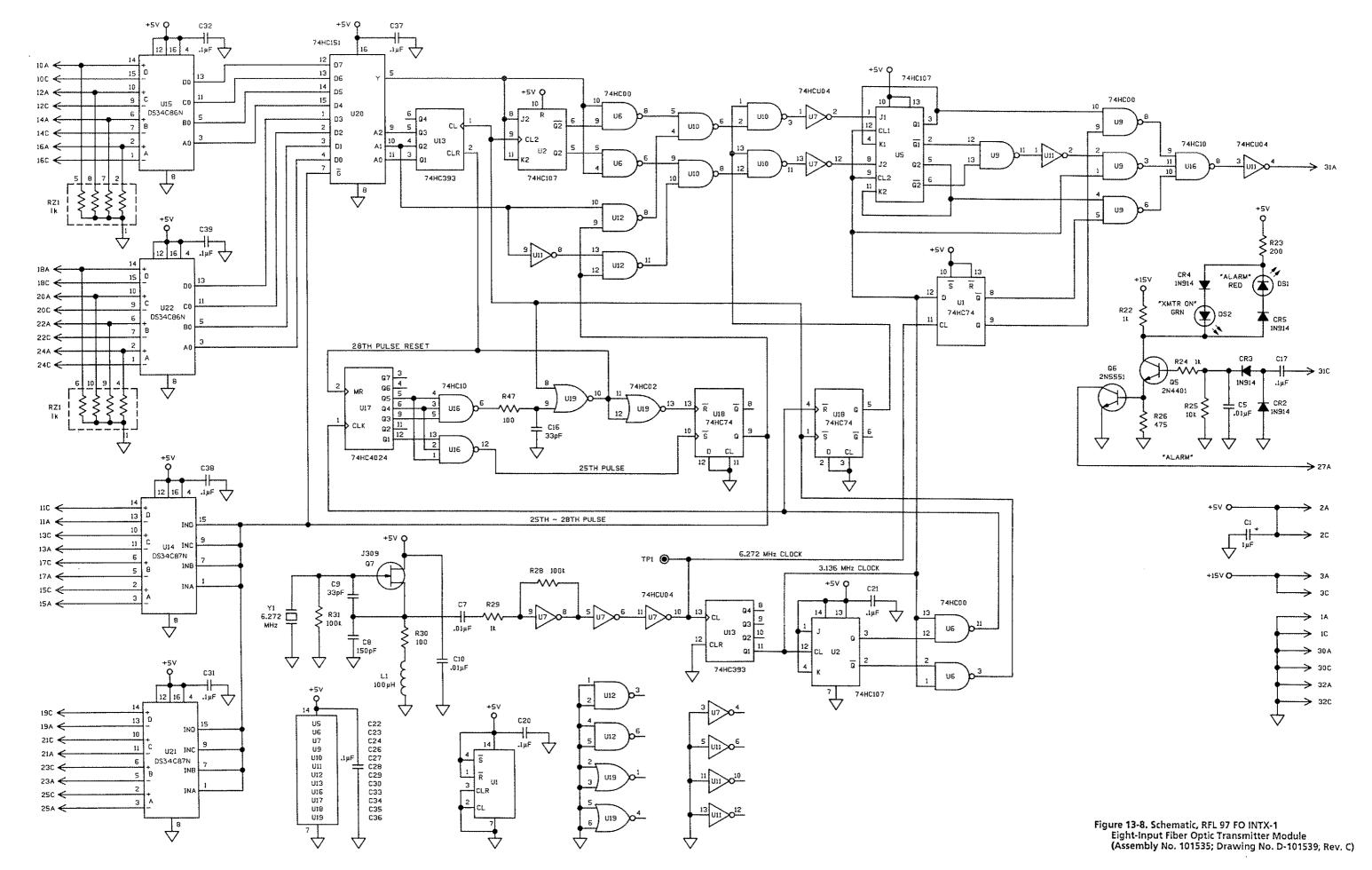

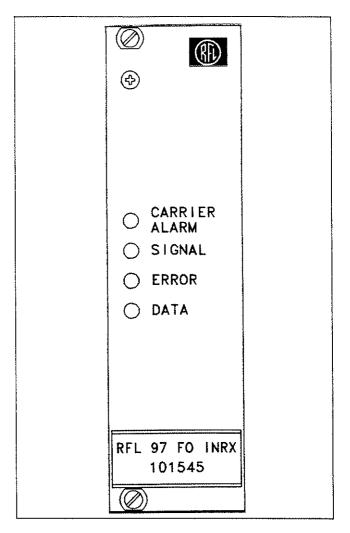

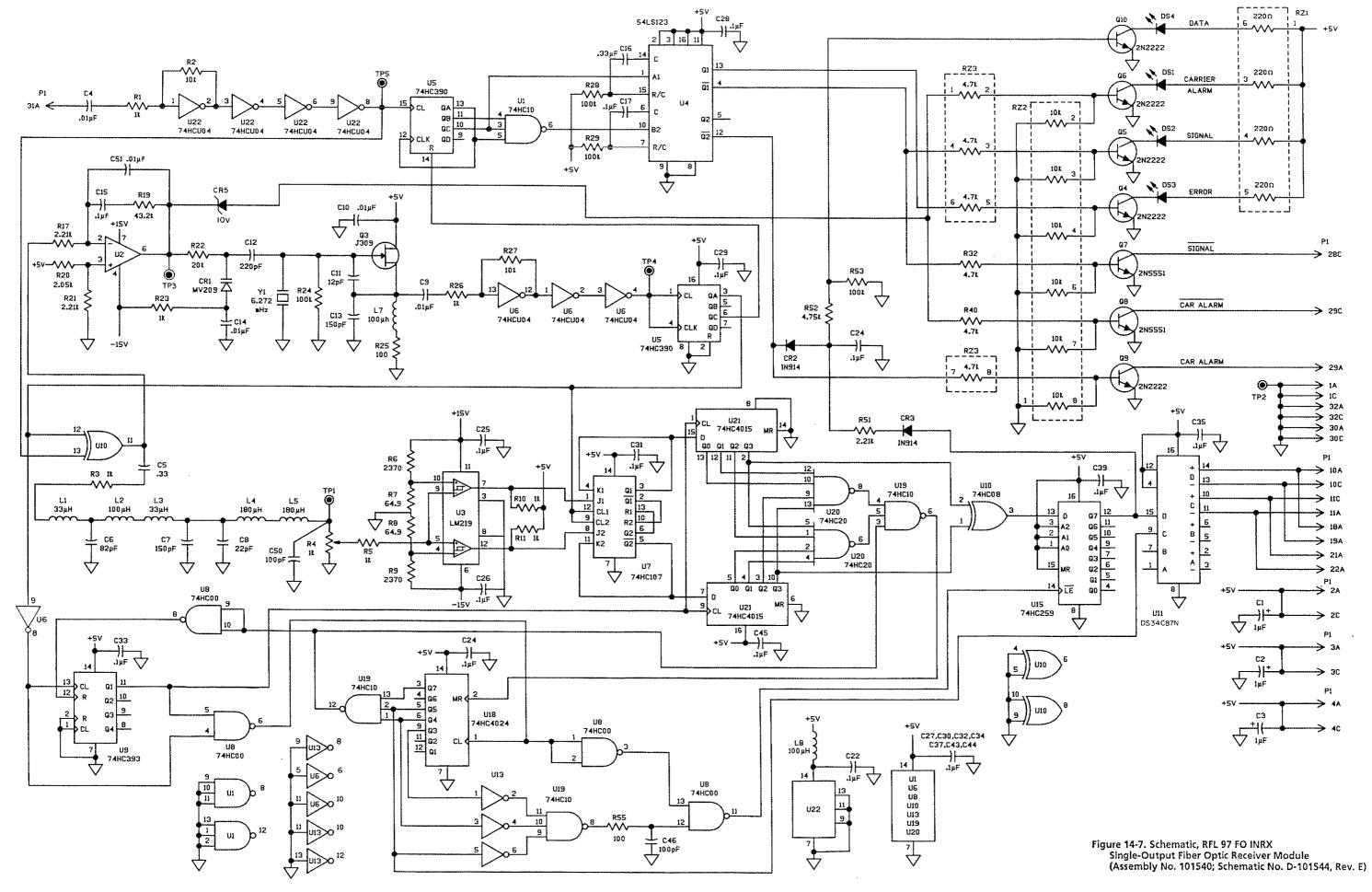

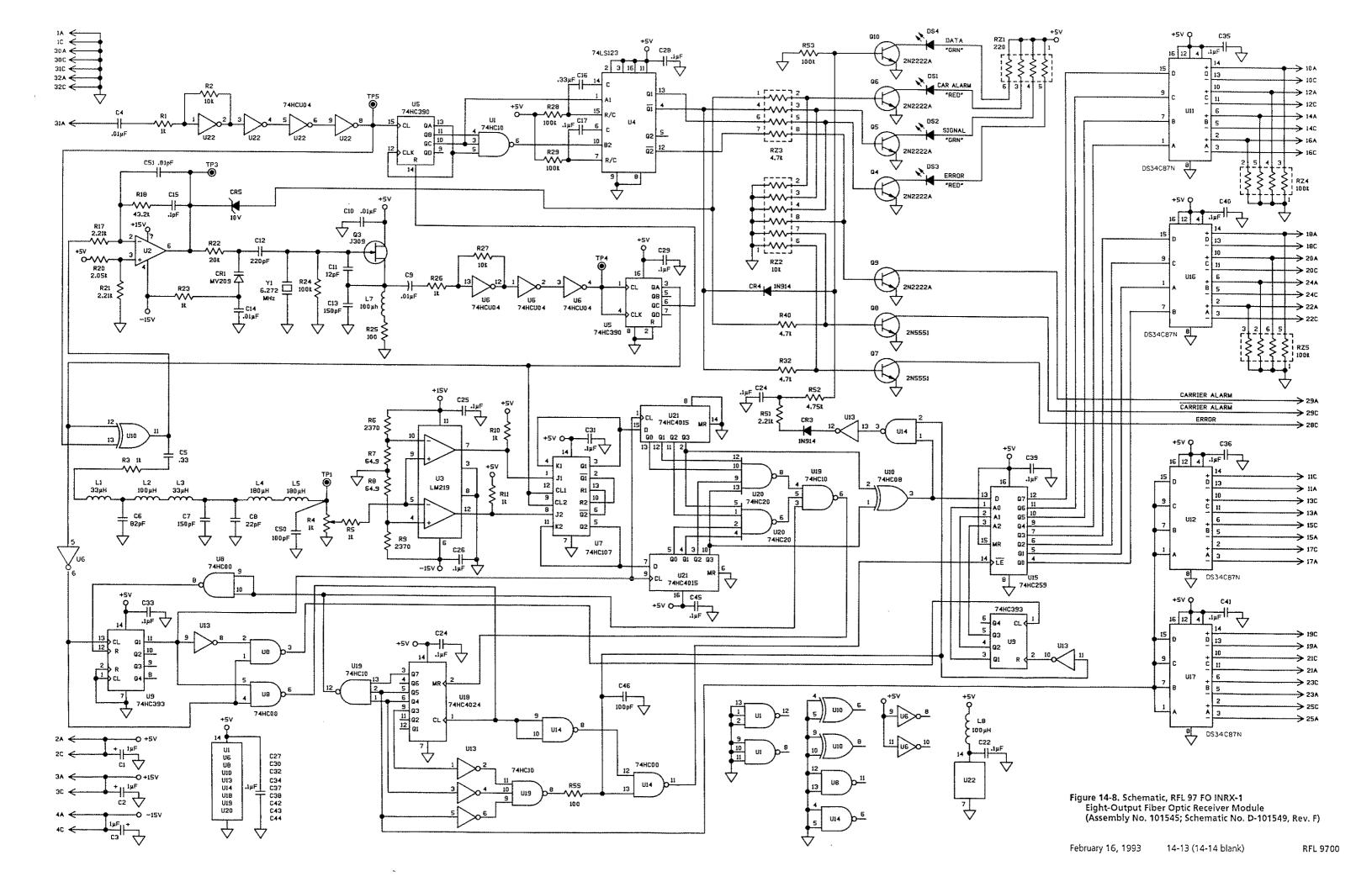

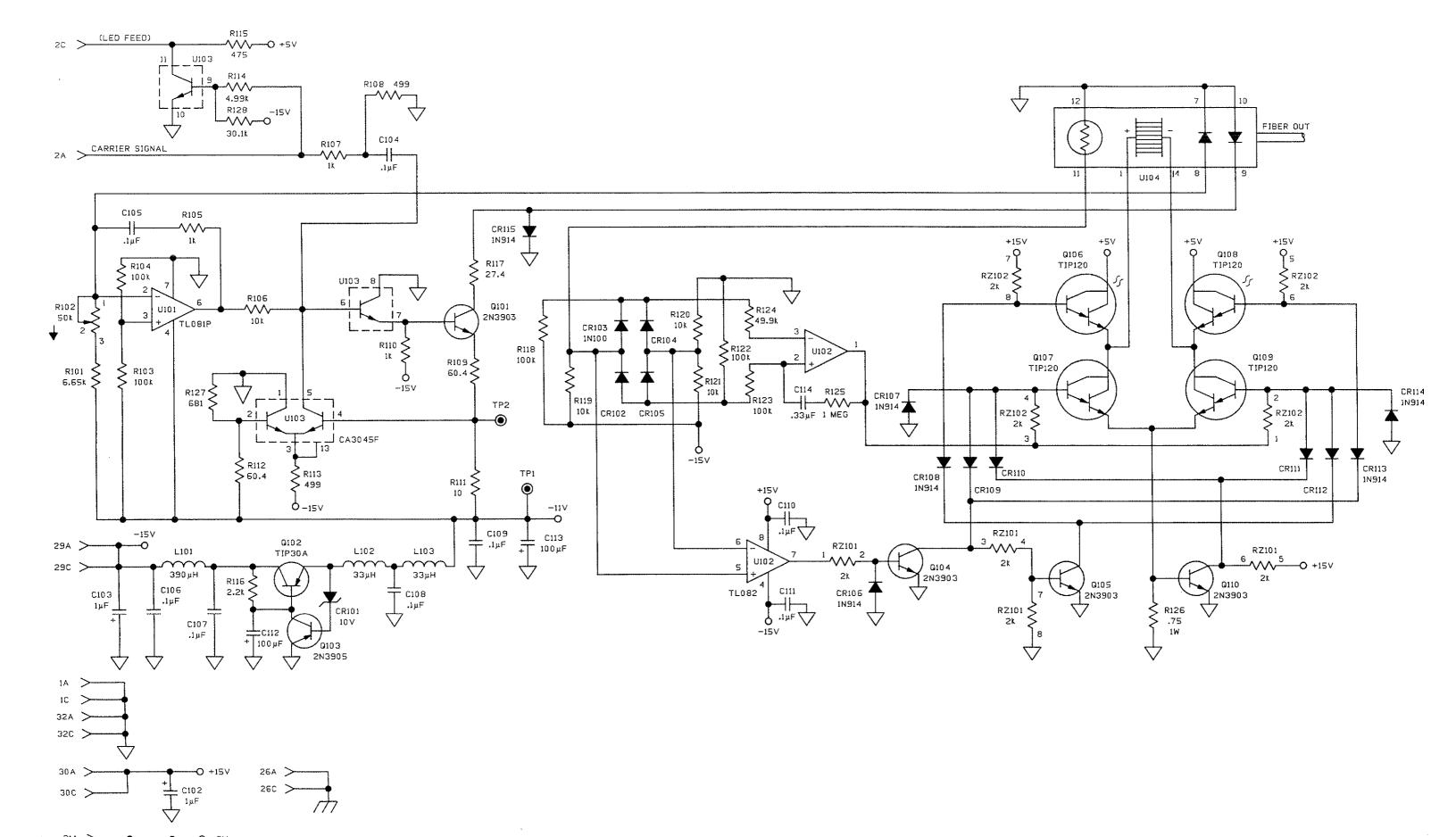

| Section 14. FIBER OPTIC RECEIVER MODULES                                                                                                                                                                                         |       | 18.1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                      | 18-1  |

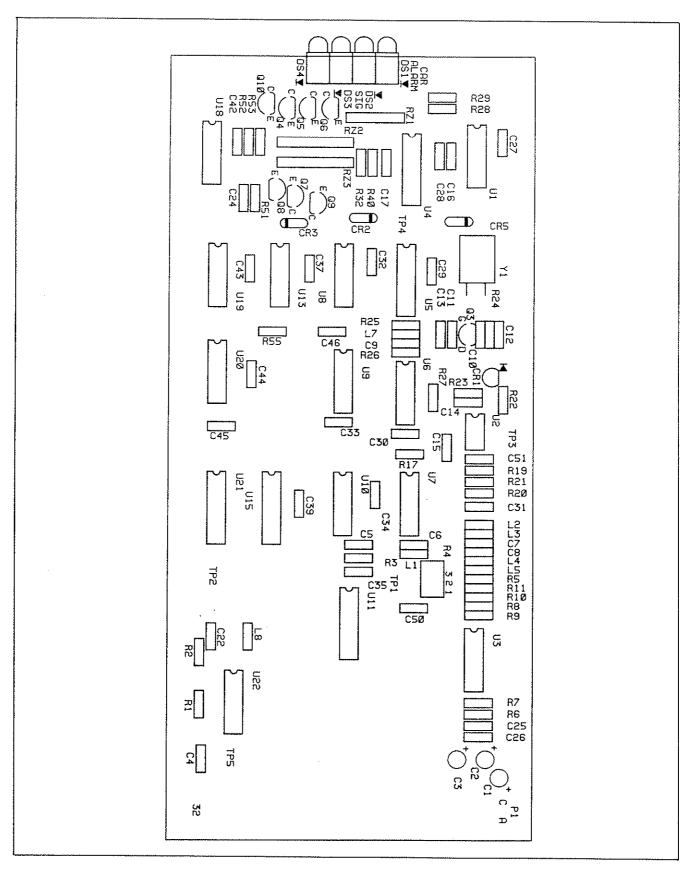

| Section 14. FIBER OPTIC RECEIVER MODULES  14.1. DESCRIPTION  14.2. SPECIFICATIONS  14.3. THEORY OF OPERATION                                                                                                                     | 14-1  | 18.2. RFL 97 449 MUX RS-449 MULTIPLEXER PANEL                                                                                                                                                                                                                                                                                                                                           | 18-1  |

| 14.2. SPECIFICATIONS                                                                                                                                                                                                             | 14-1  | 18.3. AUXILIARY VOICE/DATA SYSTEM                                                                                                                                                                                                                                                                                                                                                       | 18-1  |

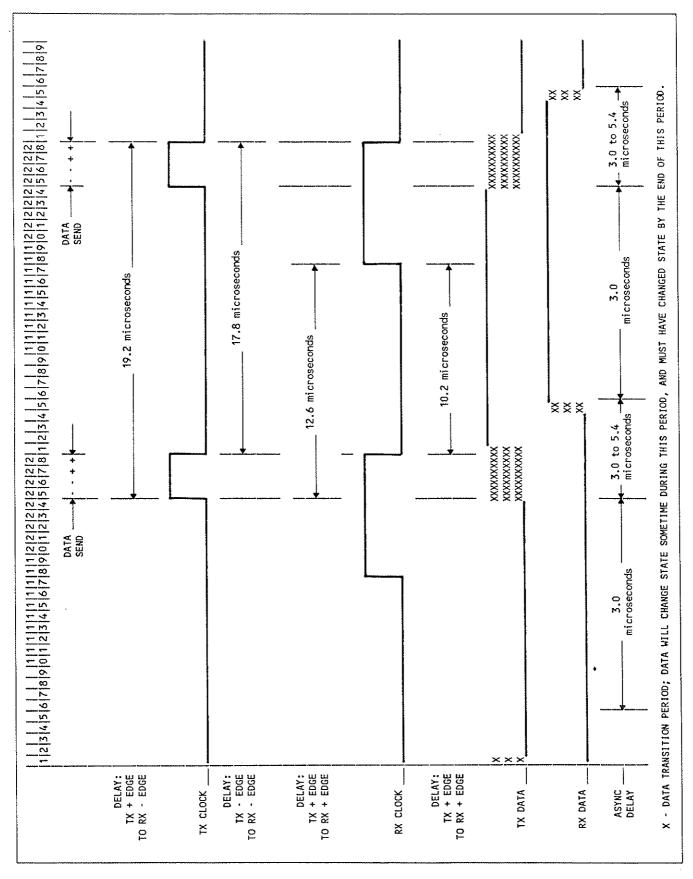

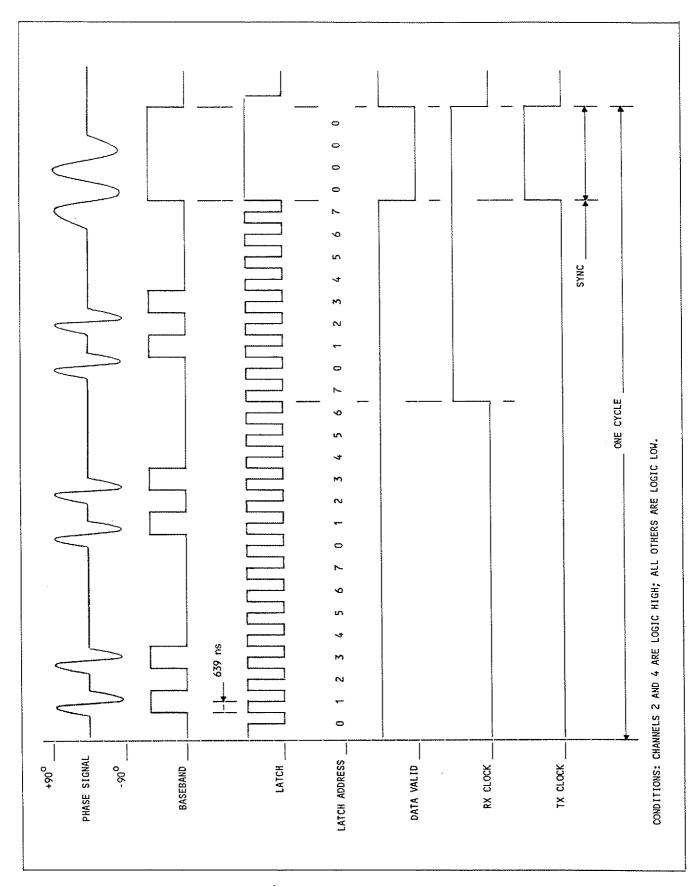

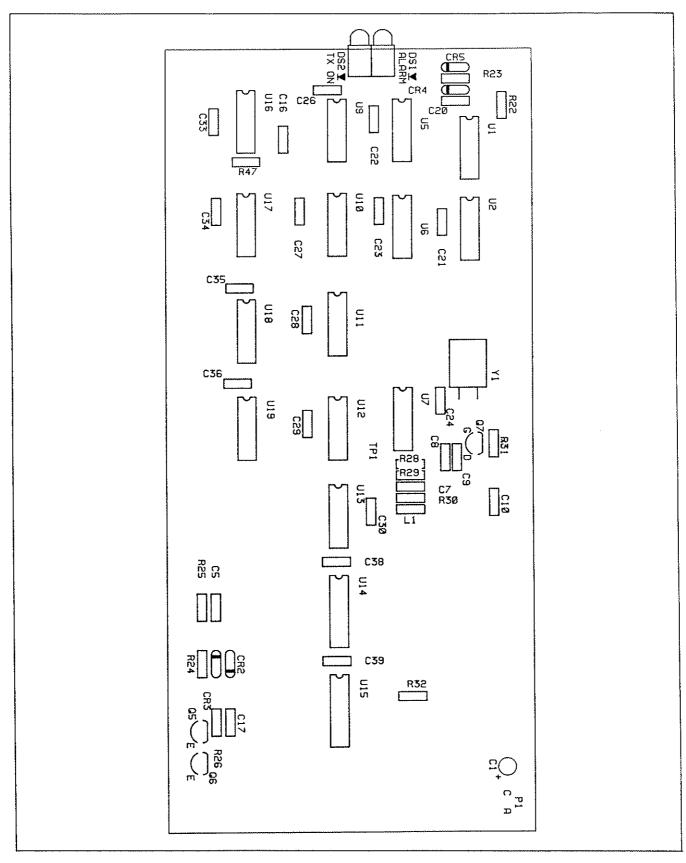

| 14.3. THEORY OF OPERATION                                                                                                                                                                                                        | 14-2  | 18.3.1. RFL 97 VOICE Voice Module                                                                                                                                                                                                                                                                                                                                                       | 18-1  |

|                                                                                                                                                                                                                                  | _     | 18.3.2. RFL 97 DATA Data Module                                                                                                                                                                                                                                                                                                                                                         | 18-1  |

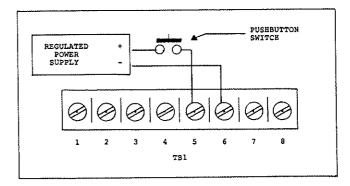

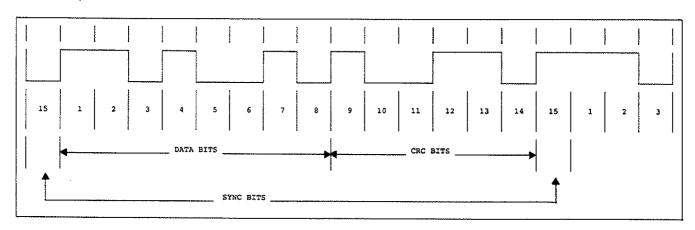

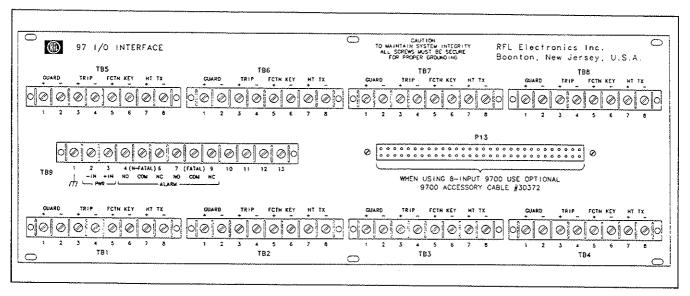

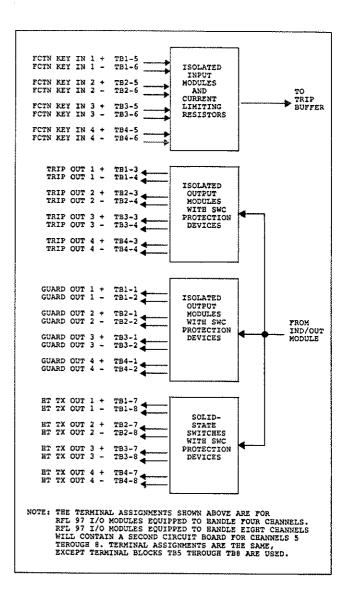

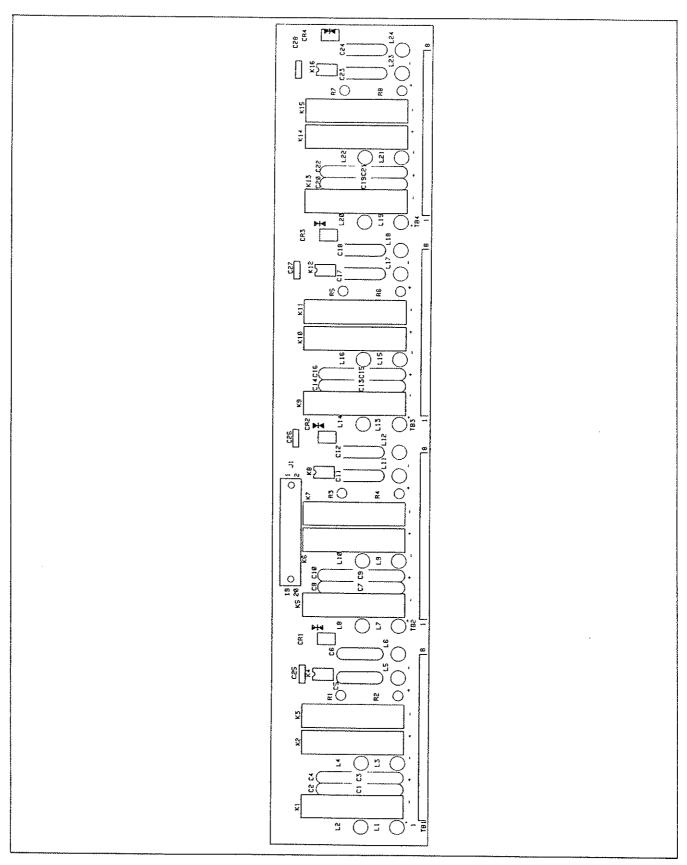

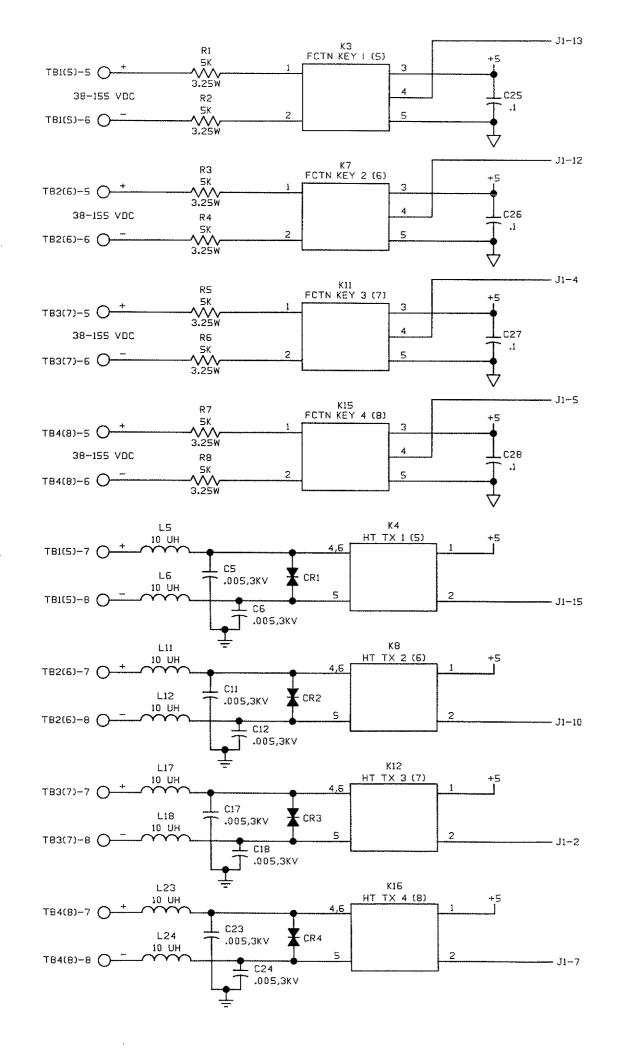

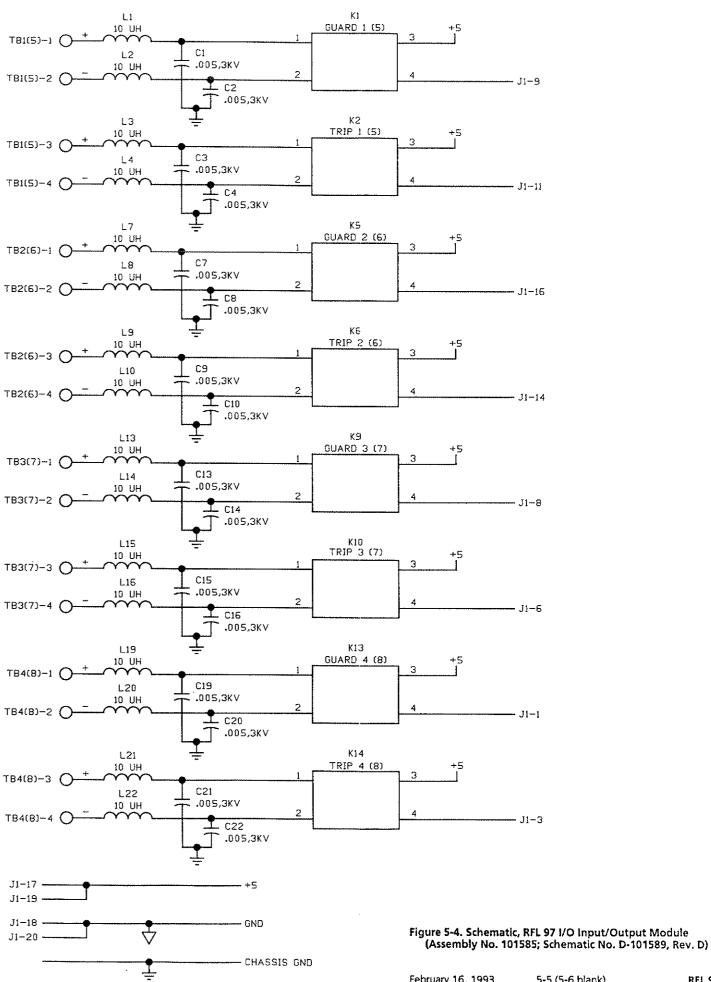

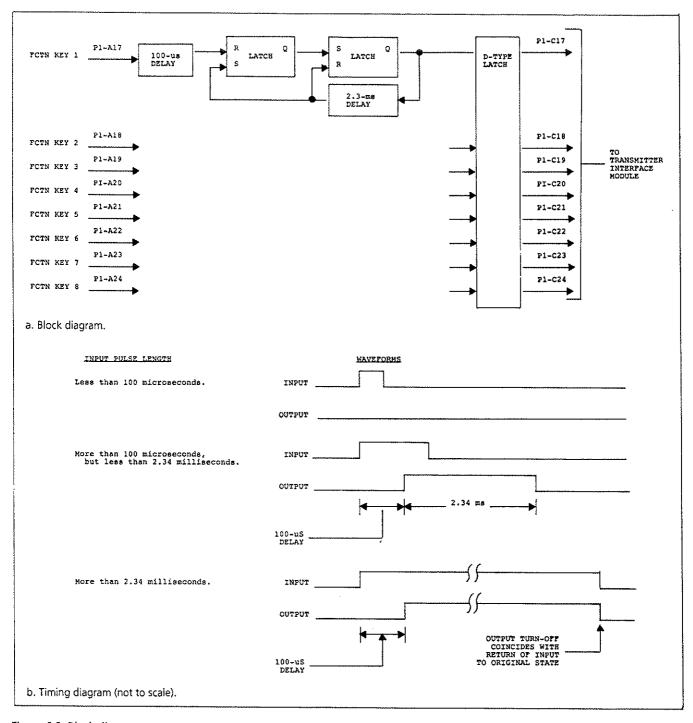

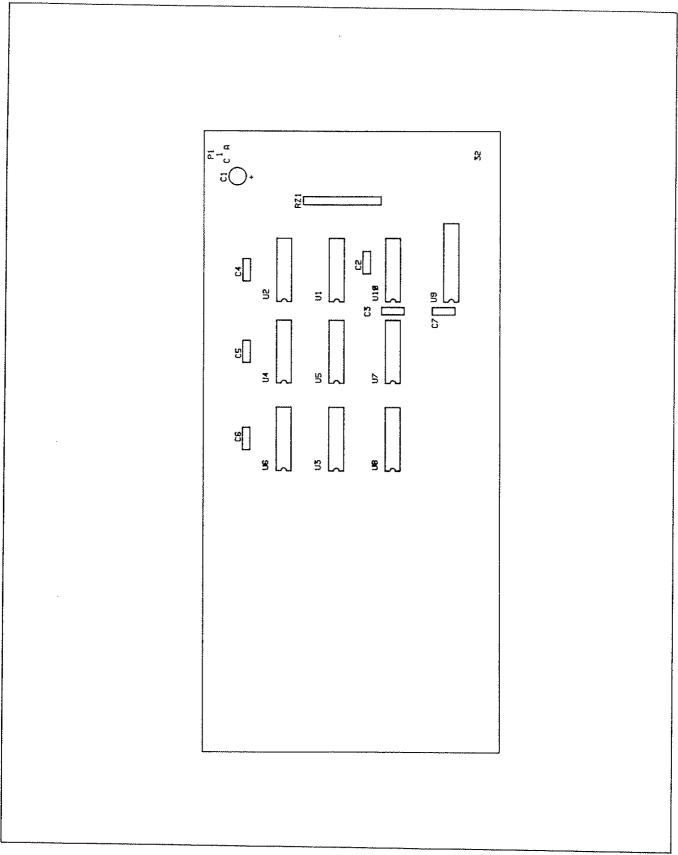

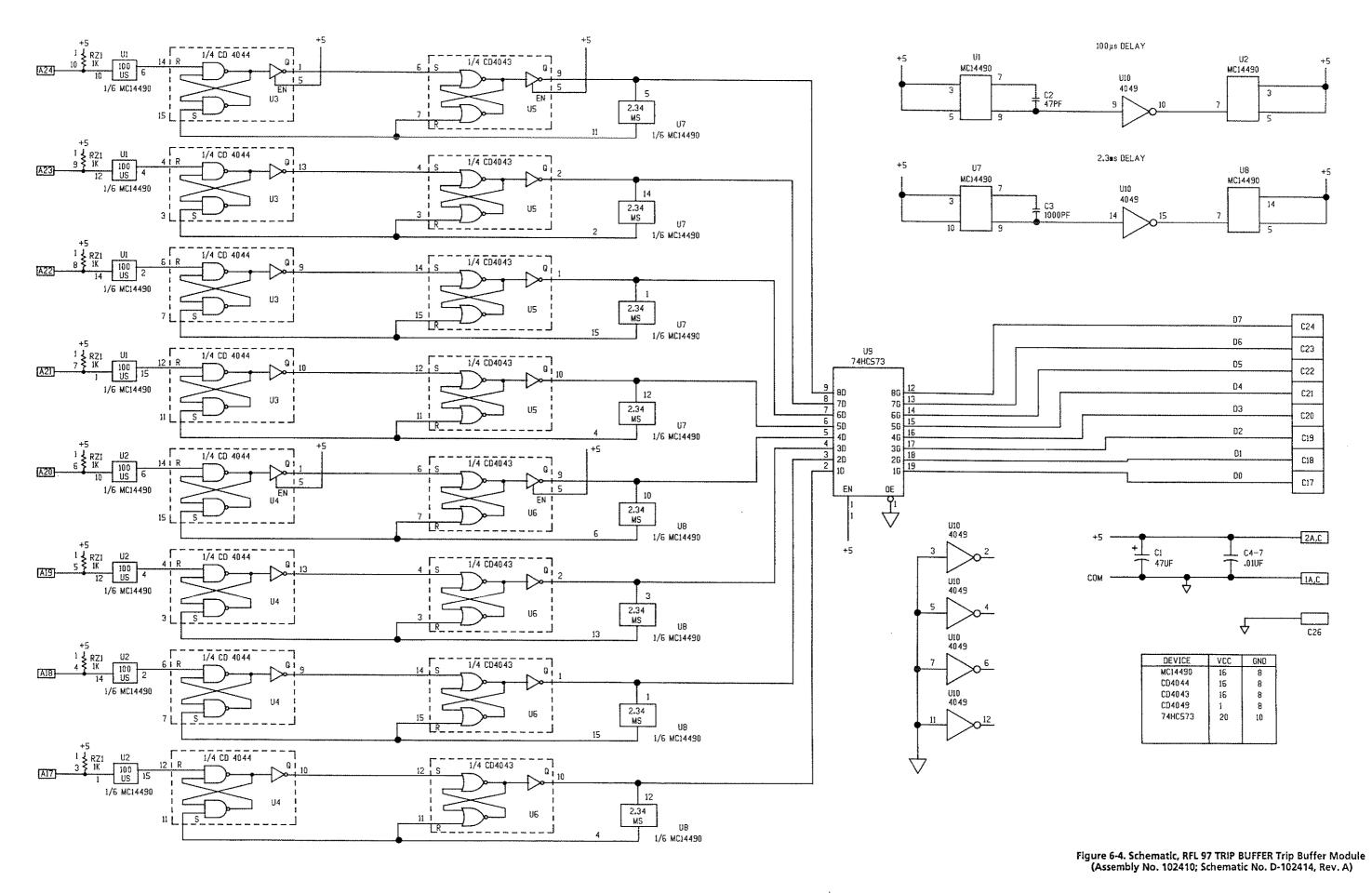

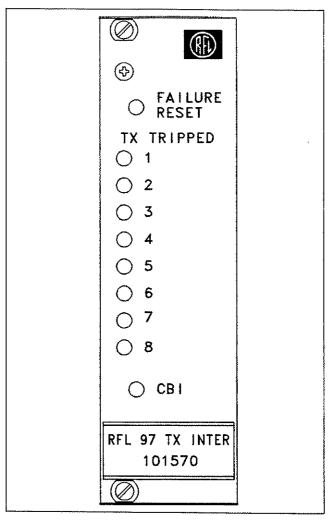

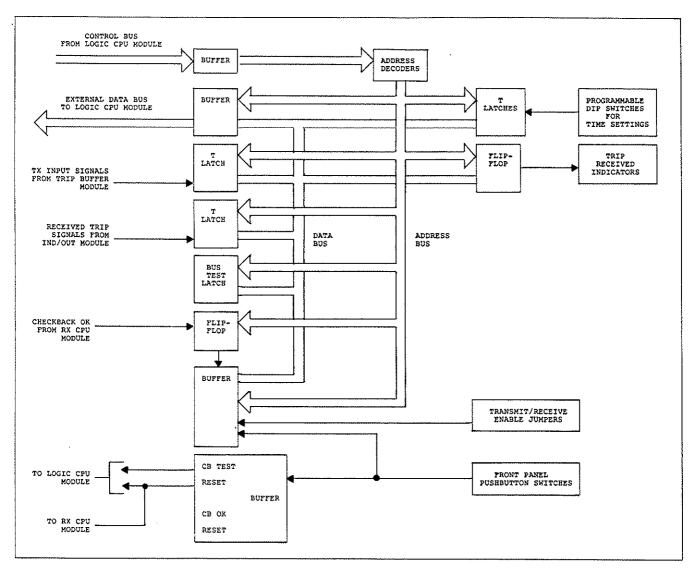

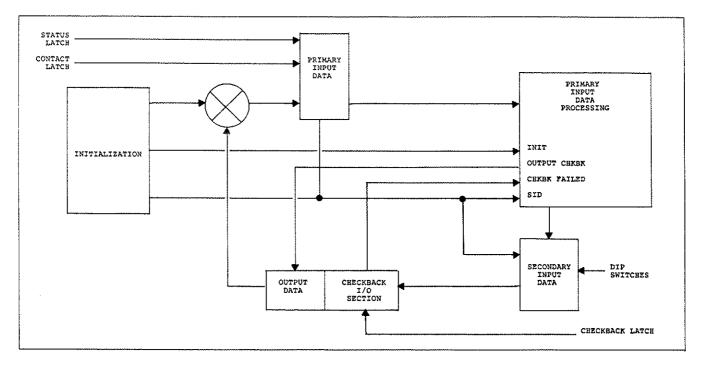

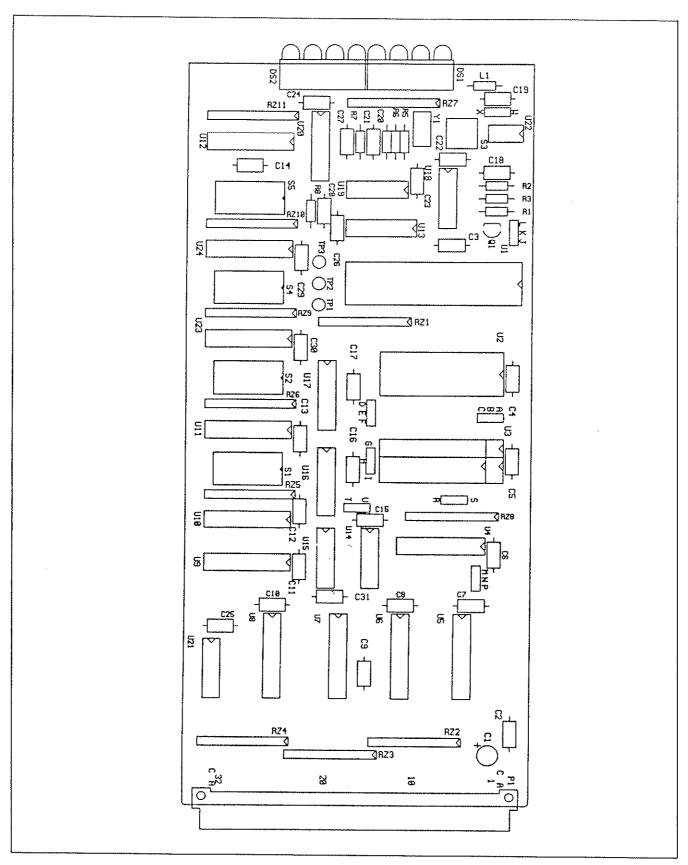

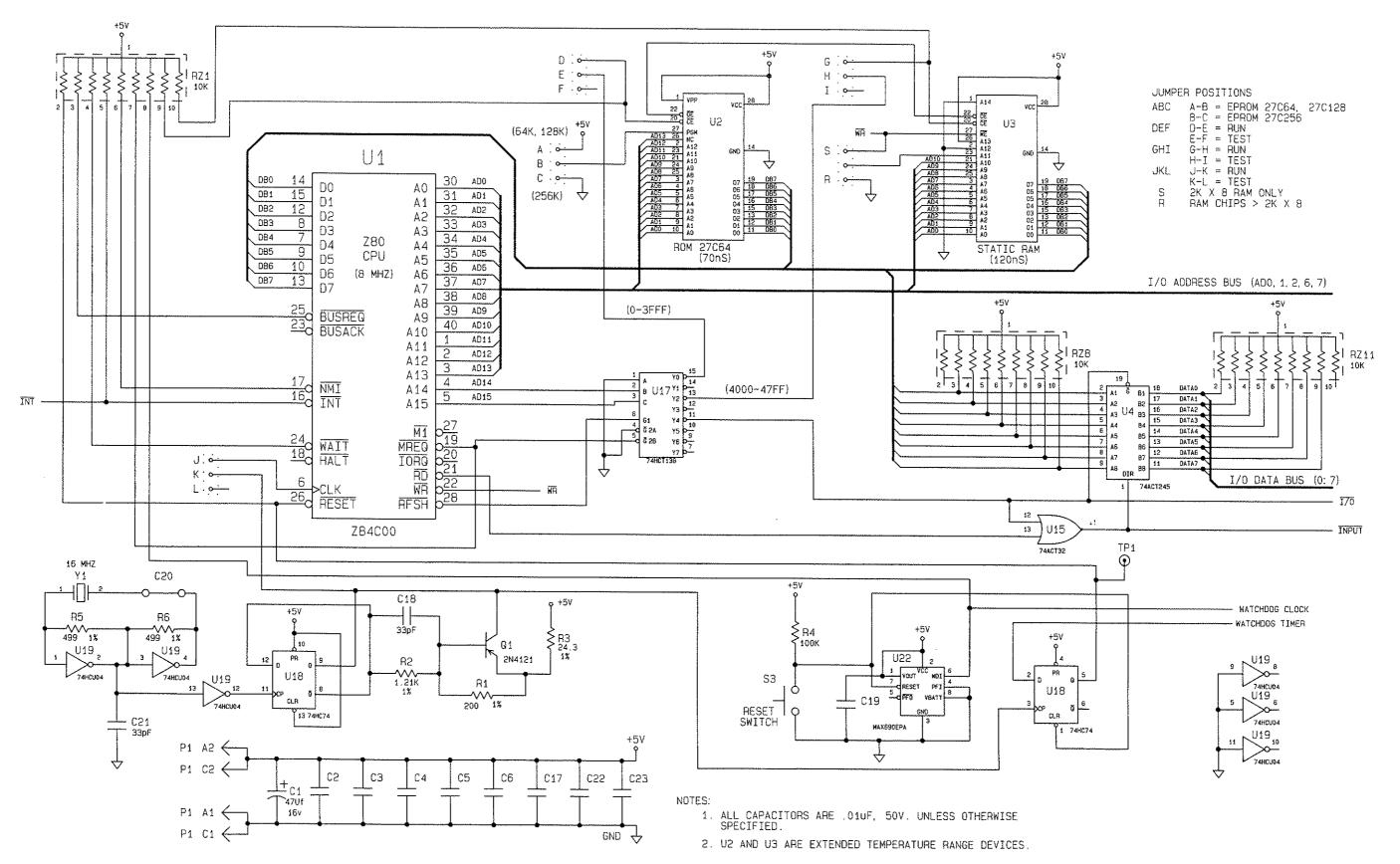

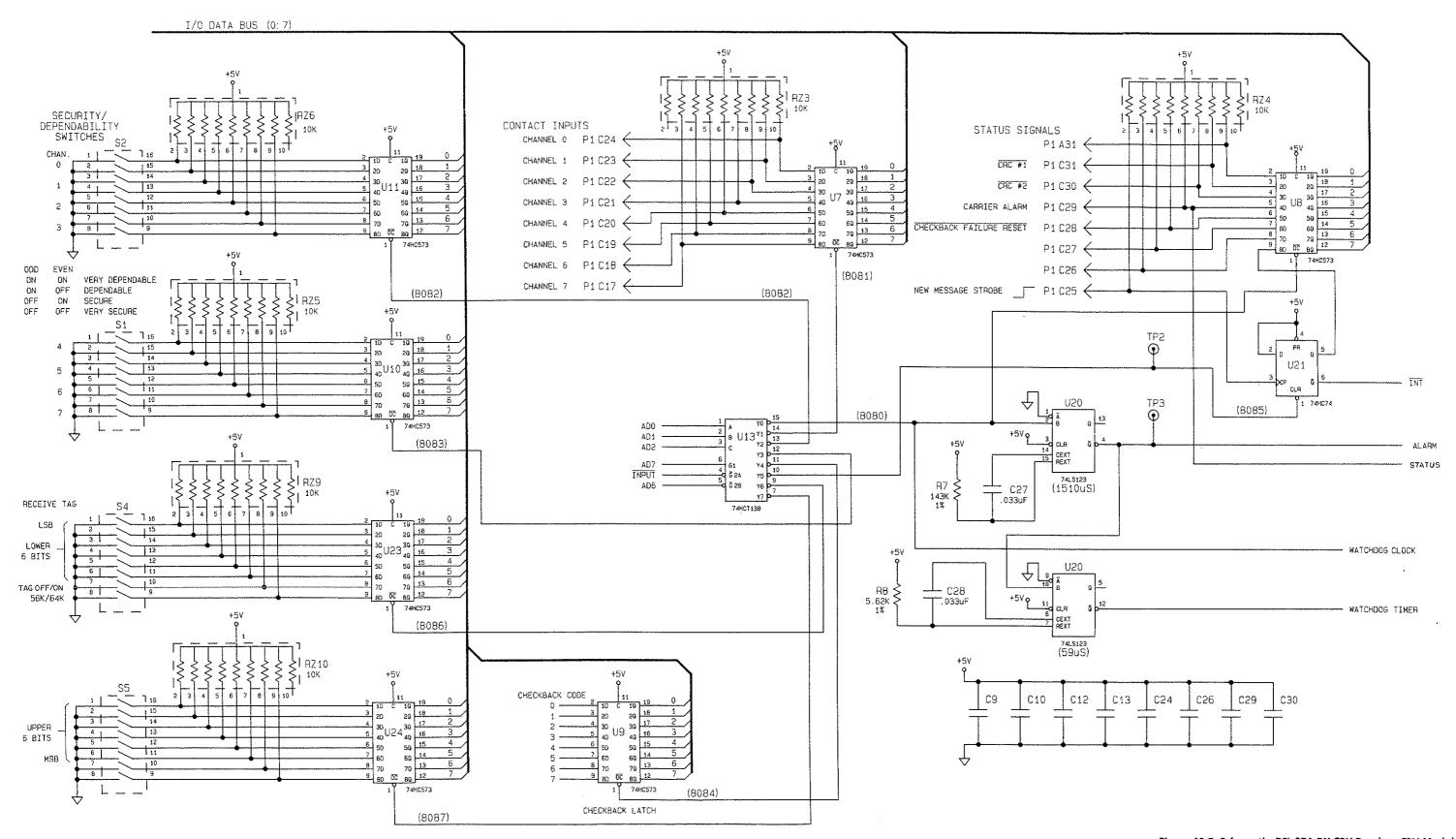

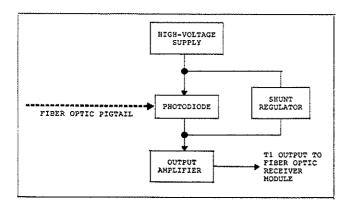

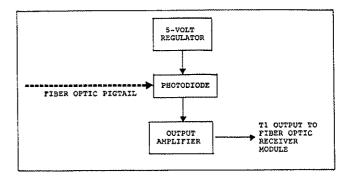

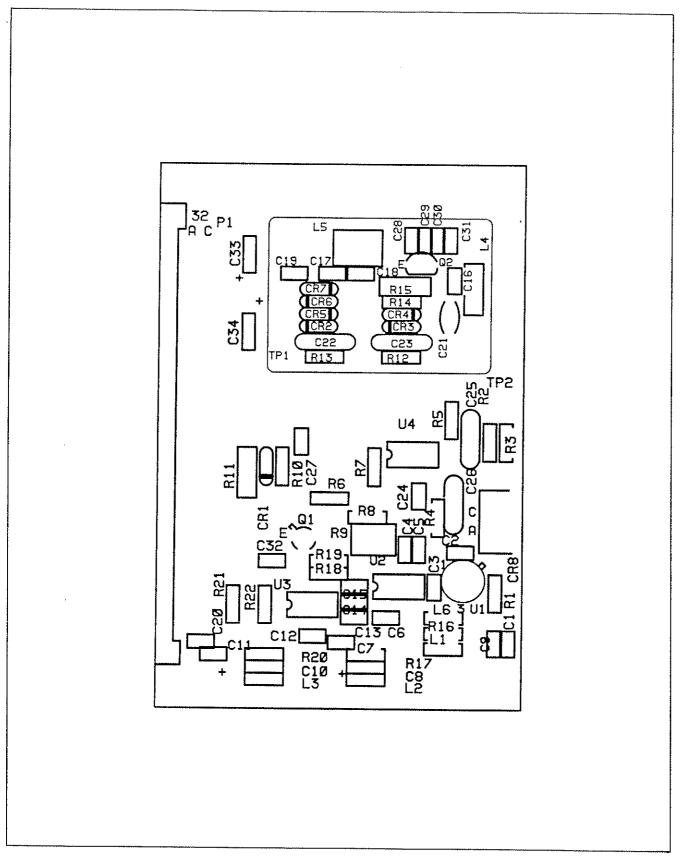

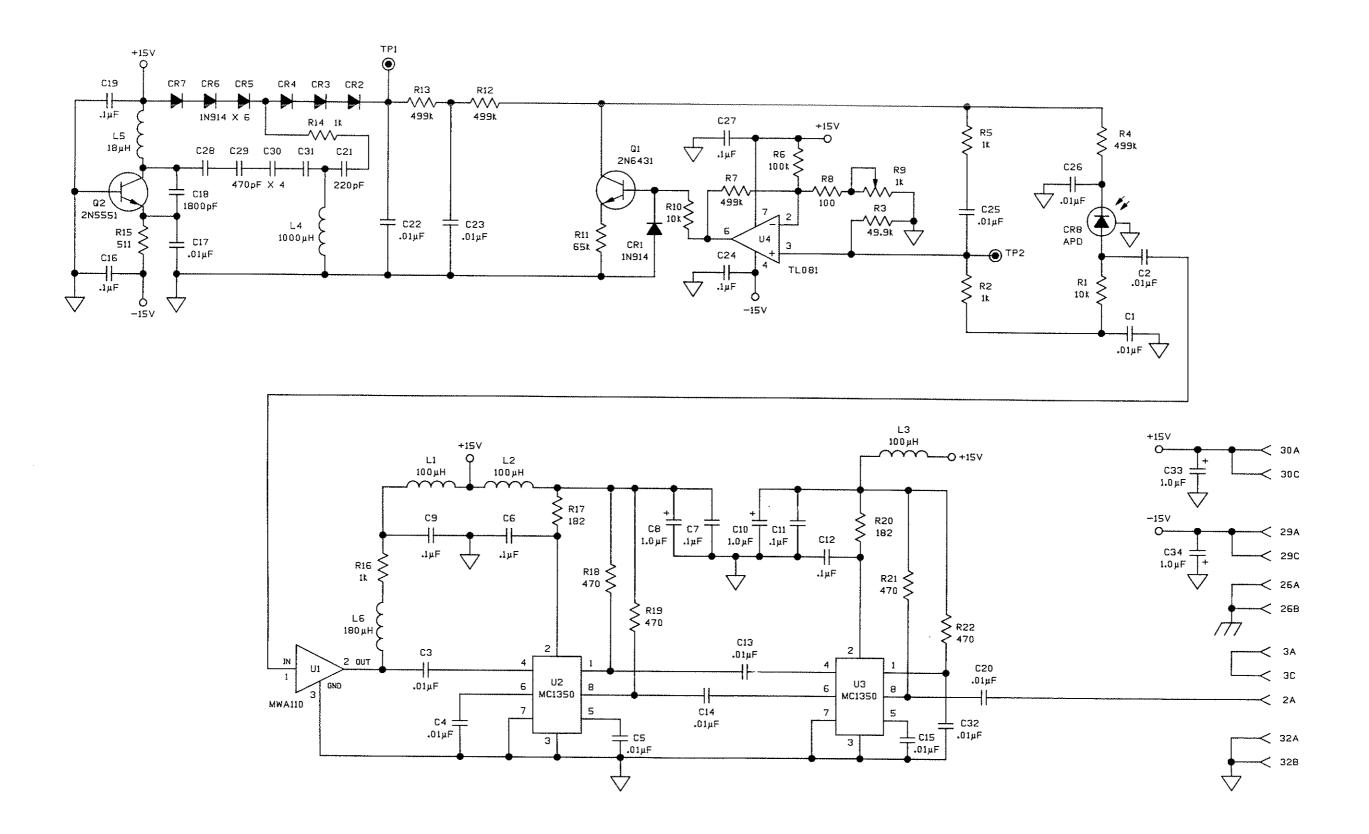

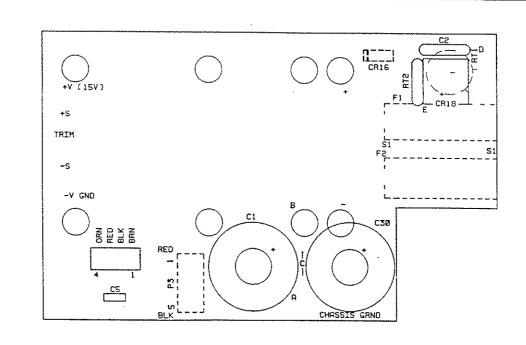

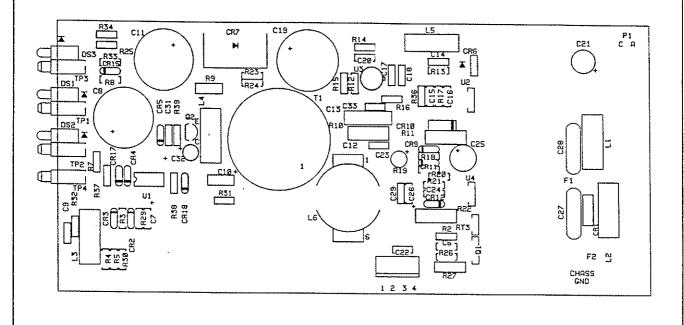

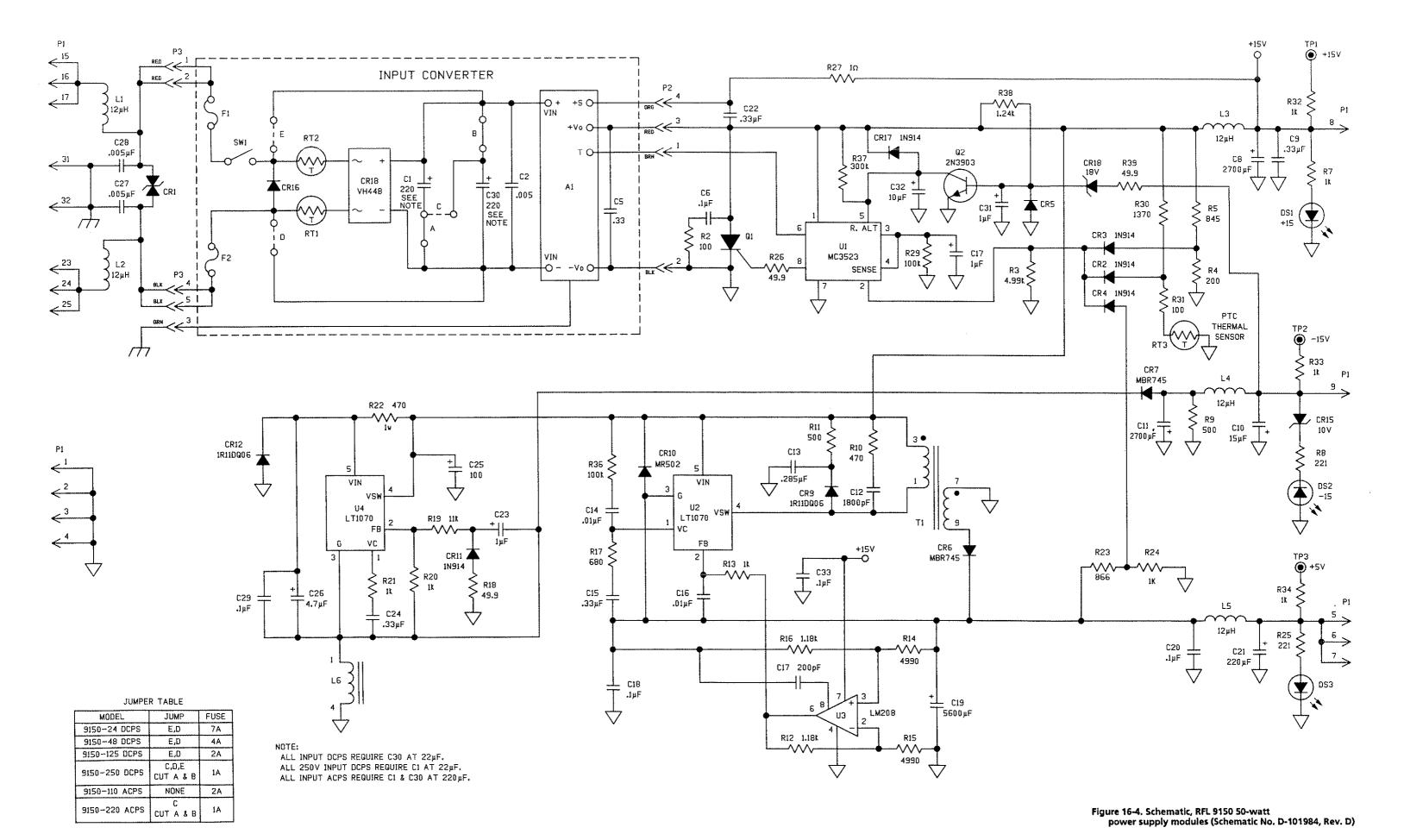

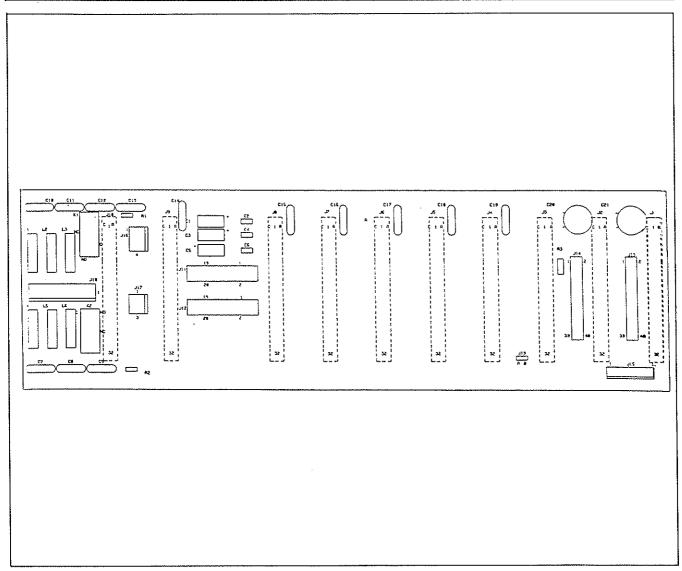

|                                                                                                                                                                                                                                  |       | 18.3.3. RFL 97 1U CHAS Chassis                                                                                                                                                                                                                                                                                                                                                          | 18-1  |